Serdes系列总结——Xilinx serdes IP使用(三)——12G serdes

judy 在 周五, 08/12/2022 - 14:36 提交

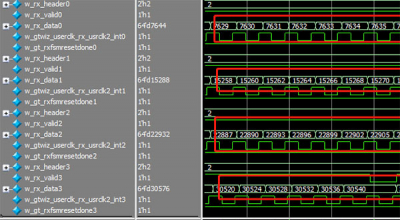

12.16512G的serdes,一个输入为64bit,输出为64bit的6664B编码的4对serdes例程,参考时钟为122.88MHz

12.16512G的serdes,一个输入为64bit,输出为64bit的6664B编码的4对serdes例程,参考时钟为122.88MHz

无论是FPGA开发还是芯片开发,其中一个重要的环节就是复位设计,本文主要说明FPGA的复位设计

数组在RTL中映射为memory,一般HLS会自动决定最合适的memory,但也支持通过RESOURCE指令具体的memory实现

研究7系列MMCME2_ADV原语,看能否自己对MMCME2_ADV封装,这样避免工程在不同器件及版本之间切换

满足设计中的时序要求本身可能很困难,所以生成 100% 可重复的时序设计似乎是不可能的。

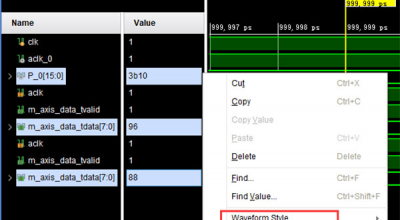

本文先介绍集中PL与PS的通信方法,然后重点介绍通过DMA实现PS与PL通信。

FIFO 通常用于跨时钟域,因此是双时钟设计。换句话说,该设计使用两个时钟

10.1376G的serdes,一个输入为64bit,输出为64bit的6664B编码的4对serdes例程,参考时钟为153.6MHz

在FPGA的设计里,RR(Round-Robin)调度是一个非常重要的话题。所谓RR调度就是从多个队列中公平地选一个队列进行处理。

本实验要完成利用vivado中的DDS IP核对两个正弦波进行混频,实现数字下变频或者上变频。