Vivado HLS从HDL到模型和C的描述(1):从运行一个程序开始

judy 在 周三, 02/16/2022 - 11:57 提交

先从运行一个创建一个项目开始吧。

先从运行一个创建一个项目开始吧。

在Vivado中,可能由于某些逻辑输入悬空而导致Implementation的opt_design时会错

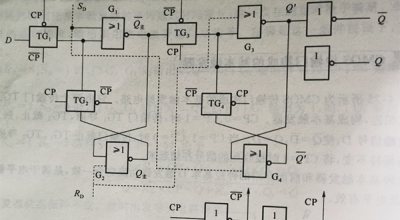

同步电路系统设计将系统状态的变化与时钟信号同步,并通过这种理想化的方式降低电路设计难度。同步电路设计是FPGA设计的基础。但是伴随着集成电路的微缩化和大规模化,同步式电路的一些问题也显现出来。

在开发FPGA绑定管脚时,经常会看到HP Bank、HR Bank和HD Bank,它们分别是什么意思?分别可以适用于哪些应用个?

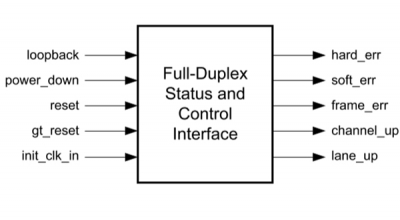

IP是什么?简单来讲,IP就是Xilinx或者第三方开发者把自己的逻辑模块封装成一个黑盒子,然后拿出来给别人用。那什么又是黑盒子?黑盒子就是你看不到里面的东西,你只能看到外面的接口。

FPGA综合和物理实现工具产生许多种报告,包含了错误和警告、逻辑利用、设计频率、时序、时钟等信息。需要设计者了解大量有关设计工具的知识才能阅读报告,以及迅速找到所需信息

本篇将重点学习解读后面三章内容:设计约束、设计实现和设计收敛。

Aurora 协议是一个用于在点对点串行链路间移动数据的可扩展轻量级链路层协议(由Xilinx开发提供)。这为物理层提供透明接口,让专有协议或业界标准协议上层能方便地使用高速收发器

本文主要参考UG949,进行重点阐述。

7系列设备中的OSERDESE2是专用的 并-转-串 转换器,使用特定的时钟和逻辑资源设计来使得高速源同步接口实现变得容易。每个OSERDESE2模块都包含一个特定的串化器(serializer)用于数据和三态(3-state)控制。