Petalinux 加速axi-dma内核驱动缓冲区读过程

judy 在 周一, 12/20/2021 - 11:29 提交

Petalinux 加速axi-dma内核驱动缓冲区读过程

Petalinux 加速axi-dma内核驱动缓冲区读过程

一个工程师有关FPGA项目的9个感言

本文介绍目前常见的几种可以提高机器学习模型的可解释性的技术,包括它们的相对优点和缺点。

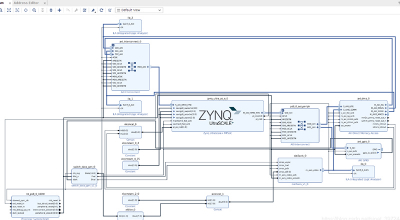

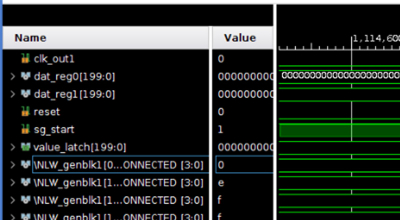

实验任务:将输入数据(data_in)存入ddr,然后读出,验证输入输出数据是否相等。

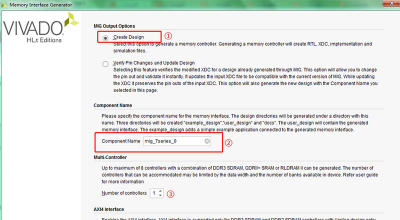

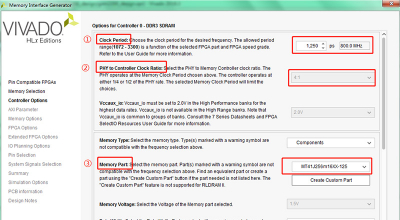

干货来了,用DDR搬砖,只需要会用IP就好,Xilinx官方YYDS!

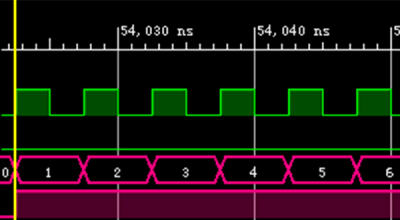

采用FPGA的CARRY4进位单元,每个CARRY4的COUT连接到下一个CARRY4的CIN,这样级联起来,形成延时链;每个COUT做为抽头输出到触发器,通过本地时钟进行数据采样

对FPGA而言,时钟就是脉搏,必须理解透彻!

在我之前写的FPGA时序约束教程中,有一篇中讲到了虚拟时钟,但文中对虚拟时钟的应用介绍的还不够详细,因此这里我们再对虚拟时钟做一个更加细致的介绍。

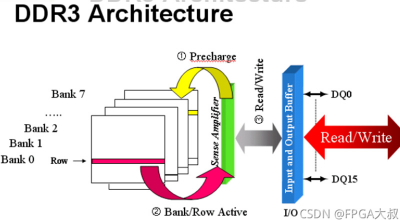

DDR3全称double-data-rate 3 synchronous dynamic RAM,即第三代双倍速率同步动态随机存储器。所谓同步,是指DDR3数据的读取写入是按时钟同步的

Xilinx FPGA MicroBlaze使用AXI 1G/2.5G Ethernet Subsystem(= Tri Mode Ethernet MAC + AXI Ethernet Buffer)以太网IP核驱动RTL8211FD千兆网口,并使用lwip2.1.2协议栈建立http服务器,支持IPv6