关于AXI4-FULL总线 多通道传输相同数据时,合并生成一组数据并对齐的研究讨论

judy 在 周五, 12/31/2021 - 09:31 提交

对于AXI4-FULL总线时,握手信号共有5路,包括写地址,写数据,写应答,读地址,读数据。当主机burst写时,每发起一次猝发交易,需要有一笔应答对应。

对于AXI4-FULL总线时,握手信号共有5路,包括写地址,写数据,写应答,读地址,读数据。当主机burst写时,每发起一次猝发交易,需要有一笔应答对应。

多看一些example design之后,你就会发现都是熟悉的配方~

可能很多FPGA初学者在刚开始学习FPGA设计的时候,经常听到类似于”这个信号需要打一拍、打两拍(寄存),以防止亚稳态问题的产生“这种话,但是对这个打拍和亚稳态问题还是一知半解,接下来结合一些资料谈下自己的理解。

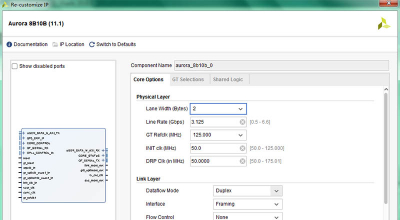

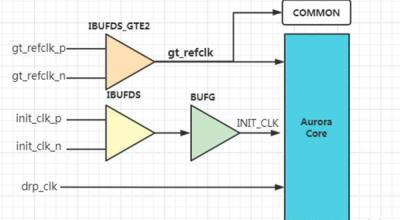

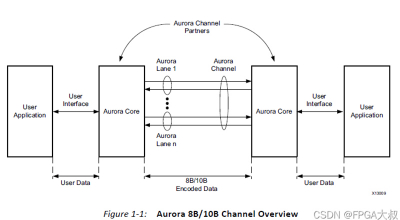

开门见山的说,跟DDR/PCIE/GTX这种复杂的IP相比,Aurora配置那是相当的简单。走着。

基于ZYNQ的multiBoot测试

对于我们使用Xilinx或其他的成熟IP而言,IP相当于一个黑匣子,内部实现的逻辑功能我们知道,但是控制不了,只能默认OK;一般而言,成熟IP都是经过反复验证和使用,确实没有什么问题。所以,IP能不能用,首先要做的就是确保时钟和复位。

使用Jtag Master调试FPGA程序时用到tcl语言,通过编写tcl脚本,可以实现对FPGA的读写,为调试FPGA程序带来极大的便利,下面对FPGA调试过程中常用的tcl语法进行介绍,并通过tcl读FIFO的例子,说明tcl在实际工程中的应用。

Aurora 广泛用于需要背板、电路板间和芯片间连接的应用。细分市场包括有线通信、存储、服务器、测试测量、工业、消费和医疗等。此外,Aurora 也可用作嵌入式处理器应用中的调试端口。

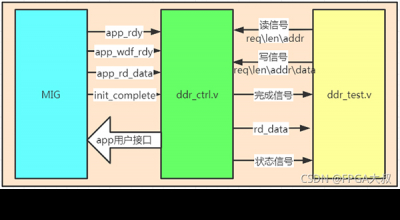

为了更方便的对DDR读写,我们对DDR再次封装成可复用的读写模块。

了解ddr的仿真模型建立