Xilinx FPGA平台GTX简易使用教程(五)GTX收发测试及示例工程介绍

judy 在 周一, 01/10/2022 - 10:52 提交

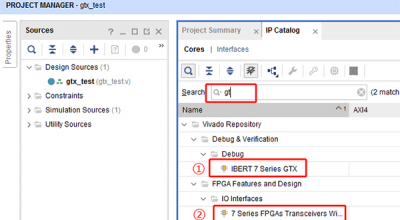

理解一个IP的用法,最好的办法就是打开官方的Example Design。 所以本文首先介绍Example Design,然后再替换成我们自己的收发测试模块,对比印证学习,差不多就能勉强把GTX给玩起来了。

理解一个IP的用法,最好的办法就是打开官方的Example Design。 所以本文首先介绍Example Design,然后再替换成我们自己的收发测试模块,对比印证学习,差不多就能勉强把GTX给玩起来了。

首先回想一下,在平常的设计中我们是不是经常采用同步复位或者异步复位的写法,这一写法似乎都已经形成了肌肉记忆----每次我们写always块的时候总是会对所有的寄存器写一个复位赋初值的语句。

作为一名初学者,也曾被GTX一堆信号搞得头晕脑胀,在学习了各位大佬的文章后,结合自己的理解和实践,整理这一系列快速上手的GTX使用教程。

IBUFDS、和OBUFDS都是差分信号缓冲器,用于不同电平接口之间的缓冲和转换。IBUFDS 用于差分输入,OBUFDS用于差分输出。

复位与初始化部分其实还挺复杂,还好GTX已经帮我们做好了,不想麻烦的直接跳到文末看结论~~~不过了解下也挺有意思的~~

模块复用是逻辑设计人员必须掌握的一个基本功,通过将成熟模块打包成IP核,可实现重复利用,避免重复造轮子,大幅提高我们的开发效率。

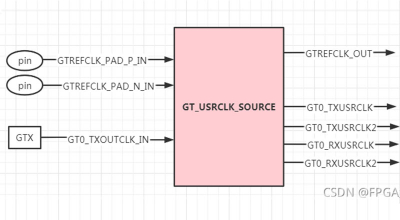

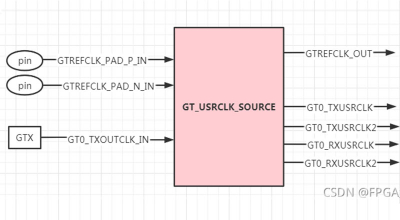

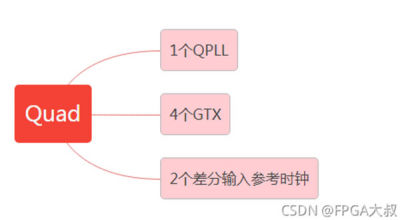

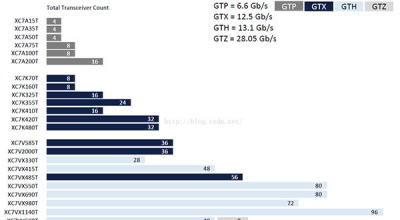

时钟就是脉搏,能否工作全靠它!话不多说,直接上干货!文中全部使用GTX代指GT Transceiver,同样适用于GTH。

面积通常指一个设计消耗FPGA/CPLD的逻辑资源的数量,通常用可消耗的FF(触发器)和LUT(查找表)来衡量。速度指设计在芯片上稳定运行所能达到的最高频率,这个频率由设计的时序状况来决定,以及设计满足的时钟要求

理解GTX的必备姿势,学起来!

FIFO最常被用来解决写、读不匹配的问题(时钟、位宽),总结下来,其实FIFO最大的作用就是缓冲。既然是缓冲,那么就要知道这个缓存的空间到底需要多大。