本文转载自:FPGA大叔的博客

实验目的:

了解ddr的仿真模型建立。

一、Example Design

每当我们例化了一个IP而不知道怎么使用时,优先打开官方示例example design

选中IP核,右键“OPEN IP in Example Design”,我这里是灰色的,那是因为我已经打开过了。

Example design就不讲了,主要有个数据产生模块,反正我们也用不上,我们只需要用里面的仿真模型。

不打开example design也行,直接打开example的仿真文件sim_tb_top:

代码太多了太长了我们直接往下翻到1011行:Memory Models instantiations

将ddr3_model例化部分复制到我们的tb文件里,参数找到对应的数字给替换掉:

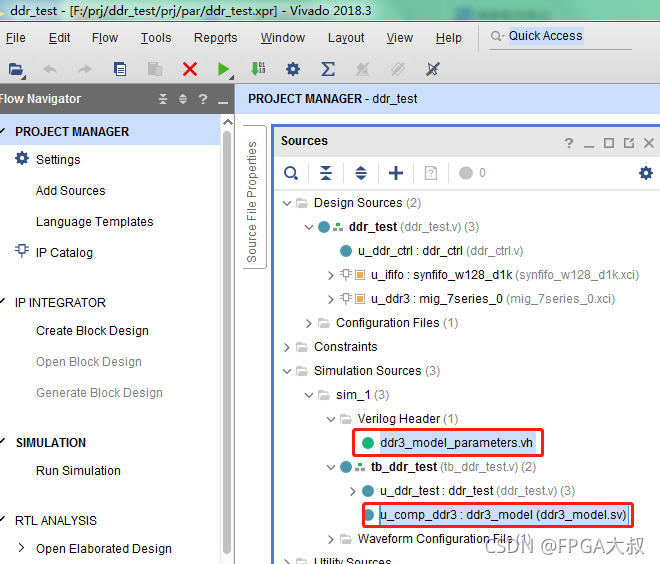

二、添加仿真文件

两个仿真文件添加到工程:

目录 : ..\sources_1\ip\mig_7series_0\mig_7series_0\example_design\sim

文件1 : ddr3_model.sv

文件2 : ddr3_model_parameters.vh

然后添加为我们的工程仿真文件。

三、Testbench的编写

添加激励,例化我们的设计ddr_test模块,例化第一节所说的ddr_model。

module tb_ddr_test();

reg sys_clk ;

reg sys_rst ;

reg [127:0] data_in ;

reg vld_in ;

reg sof_in ;

reg eof_in ;

reg [5:0] cnt ;

wire [127:0] data_out ;

wire vld_out ;

wire [14:0] ddr3_addr ;

wire [2:0] ddr3_ba ;

wire ddr3_cas_n ;

wire [0:0] ddr3_ck_n ;

wire [0:0] ddr3_ck_p ;

wire [0:0] ddr3_cke ;

wire ddr3_ras_n ;

wire ddr3_reset_n ;

wire ddr3_we_n ;

wire [15:0] ddr3_dq ;

wire [1:0] ddr3_dqs_n ;

wire [1:0] ddr3_dqs_p ;

wire init_calib_complete ;

wire [0:0] ddr3_cs_n ;

wire [1:0] ddr3_dm ;

wire [0:0] ddr3_odt ;

initial

begin

sys_clk = 0;

sys_rst = 1;

#100

sys_rst = 0;

end

always #2.5 sys_clk = ~sys_clk; //200Mhz

//用计数器来产生data_in

always @(posedge sys_clk or negedge init_calib_complete)begin

if(init_calib_complete == 1'b0)

cnt <= 6'b0;

else if(&cnt)

cnt <= cnt;

else

cnt <= cnt + 1'b1;

end

always @(posedge sys_clk or negedge init_calib_complete)begin

if(init_calib_complete == 1'b0)begin

data_in <= 128'b0;

sof_in <= 1'b0;

eof_in <= 1'b0;

vld_in <= 1'b0;

end

else begin

data_in <= 128'b0;

sof_in <= 1'b0;

eof_in <= 1'b0;

vld_in <= 1'b0;

if(cnt > 'd10 && cnt <= 'd60)begin

data_in <= data_in + 1'b1;

vld_in <= 1'b1;

end

if(cnt == 'd11)

sof_in <= 1'b1;

if(cnt == 'd60)

eof_in <= 1'b1;

end

end

ddr_test u_ddr_test(

.sys_clk (sys_clk ),

.sys_rst (sys_rst ),

.data_in (data_in ),

.vld_in (vld_in ),

.sof_in (sof_in ),

.eof_in (eof_in ),

.data_out (data_out ),

.vld_out (vld_out ),

.ddr3_addr (ddr3_addr ),

.ddr3_ba (ddr3_ba ),

.ddr3_cas_n (ddr3_cas_n ),

.ddr3_ck_n (ddr3_ck_n ),

.ddr3_ck_p (ddr3_ck_p ),

.ddr3_cke (ddr3_cke ),

.ddr3_ras_n (ddr3_ras_n ),

.ddr3_reset_n (ddr3_reset_n ),

.ddr3_we_n (ddr3_we_n ),

.ddr3_dq (ddr3_dq ),

.ddr3_dqs_n (ddr3_dqs_n ),

.ddr3_dqs_p (ddr3_dqs_p ),

.init_calib_complete (init_calib_complete),

.ddr3_cs_n (ddr3_cs_n ),

.ddr3_dm (ddr3_dm ),

.ddr3_odt (ddr3_odt )

);

ddr3_model u_comp_ddr3(

.rst_n (ddr3_reset_n ),

.ck (ddr3_ck_p ),

.ck_n (ddr3_ck_n ),

.cke (ddr3_cke ),

.cs_n (ddr3_cs_n ),

.ras_n (ddr3_ras_n ),

.cas_n (ddr3_cas_n ),

.we_n (ddr3_we_n ),

.dm_tdqs (ddr3_dm ),

.ba (ddr3_ba ),

.addr (ddr3_addr ),

.dq (ddr3_dq ),

.dqs (ddr3_dqs_p ),

.dqs_n (ddr3_dqs_n ),

.tdqs_n (),

.odt (ddr3_odt )

);

endmodule

OK,干净清爽!

开始仿真!

DDR仿真建议用modelsim哦,因为速度快!

想要知道怎么用脚本进行仿真?安排!