FPGA设计中的串并和并串转换

judy 在 周四, 01/12/2023 - 10:27 提交

串并、并串转化也是FPGA设计中常见的基本问题,相对来说比较简单

串并、并串转化也是FPGA设计中常见的基本问题,相对来说比较简单

为了更精确地进行时序分析,设计者还必须设定一些与运行环境相关的可预测变量和随机变量

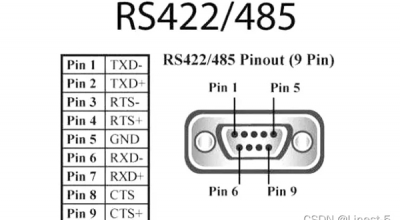

RS-232接口符合电子工业联盟(EIA)建立的串行数据通信接口标准

首先,从理论上讲,Hold Time违例,是因为时钟绕的太远,到达时间太晚

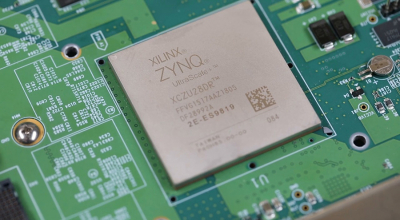

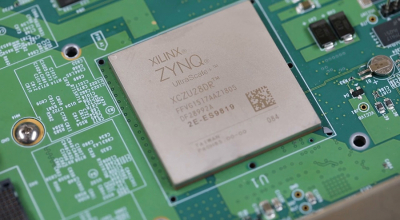

本文主要对RFSOC的时钟结构以及相关配置进行介绍,并简单介绍了关于复位的操作。

本节我们介绍FPGA收发器RX以下相关内容:RX字节和字对齐,RX弹性缓冲器。

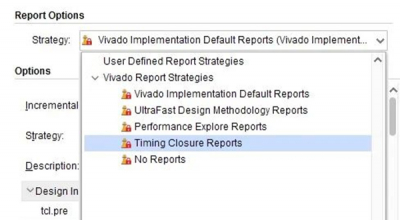

今天就通过一个简单的工程来看下如何在vivado软件中查看时序报告

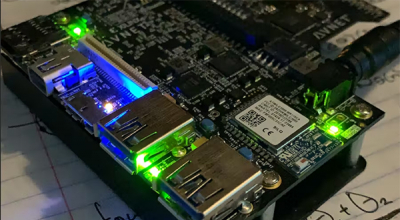

本文介绍如何使用Xilinx DDS Compiler IP并把它运行在 Ultra96 板上的可编程逻辑中

本文主要对正交调制器校正、粗延迟设置、动态更新配置、PLL以及中断处理操作进行介绍

本文我们继续介绍7系列FPGA收发器架构的RX部分内容