版权声明:本文为博主原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。

本文链接:https://blog.csdn.net/qq_37512669/article/details/90761742

软件:Vivado2017.4 板卡:Ego1 型号:xc7a35tcsg324-1

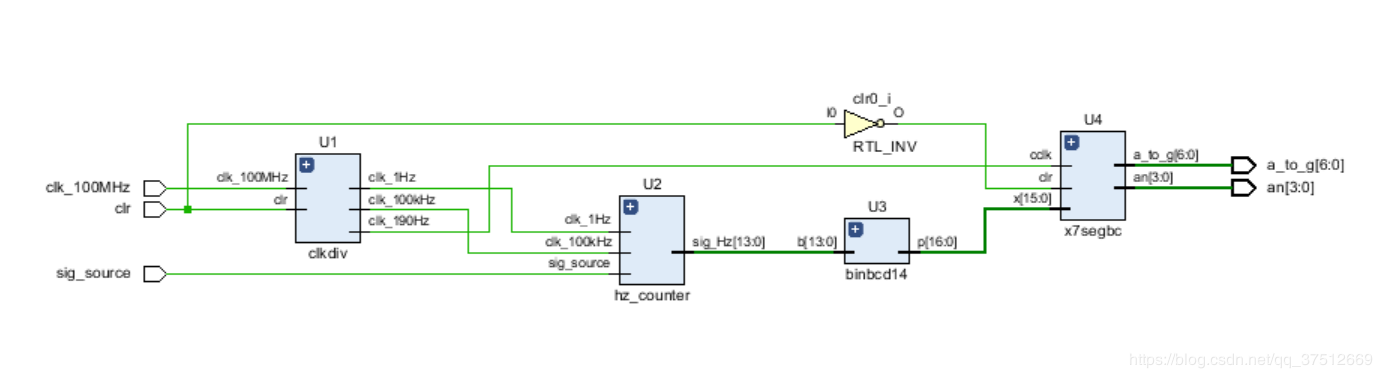

七、纯Verilog实现数字频率计

hz_counter_top.v

`timescale 1ns / 1ps

module hz_counter_top(

input wire clk_100MHz,

input wire clr,

input wire sig_source,

output wire[6:0]a_to_g,

output wire[3:0]an

);

wire[16:0]p;

wire clk_1Hz,clk_190Hz,clk_100kHz;

wire[13:0]sig_Hz;

clkdiv U1(.clk_100MHz(clk_100MHz),

.clr(clr),

.clk_100kHz(clk_100kHz),

.clk_190Hz(clk_190Hz),

.clk_1Hz(clk_1Hz)

);

hz_counter U2(.clk_100kHz(clk_100kHz),

.clk_1Hz(clk_1Hz),

.sig_source(sig_source),

.sig_Hz(sig_Hz)

);

binbcd14 U3(.b(sig_Hz),

.p(p)

);

x7segbc U4(.x(p[15:0]),

.cclk(clk_190Hz),

.clr(~clr),

.a_to_g(a_to_g),

.an(an)

);

endmodule

clkdiv.v

`timescale 1ns / 1ps

module clkdiv(

input wire clk_100MHz,

input wire clr,

output reg clk_100kHz,

output wire clk_190Hz,

output reg clk_1Hz

);

reg[25:0]count1,count2,count3;

initial

begin

count1=0;

count2=0;

count3=0;

end

always@(posedge clk_100MHz)

begin

count3<=count3+1;

if(count3==26'h1F4)

begin

count3<=0;

clk_100kHz<=~clk_100kHz;

end

end

always@(posedge clk_100MHz)

begin

count1<=count1+1;

if(count1 == 26'h2FAF07F)

begin

count1<=0;

clk_1Hz<=~clk_1Hz;

end

end

always@(posedge clk_100MHz or posedge clr)

begin

if(clr ==1)

count2 <=0;

else

count2<=count2+1;

end

assign clk_190Hz =count2[18];

endmodule

hz_counter.v

`timescale 1ns / 1ps

module hz_counter(

input wire clk_100kHz,

input wire clk_1Hz,

input wire sig_source,

output reg[13:0]sig_Hz

);

parameter N=1000000;

reg sig_state;

reg[16:0]sig_Hz_reg;

reg[16:0]sig_count;

initial begin

sig_state<=0;

end

always@(posedge sig_source)

begin

sig_state <=~sig_state;

end

always@(posedge clk_100kHz)

begin

if(sig_state)

sig_count <= sig_count+1;

else

sig_count<=0;

end

always@(negedge sig_state)

begin

sig_Hz_reg = N/sig_count;

end

always@(posedge clk_1Hz)

begin

sig_Hz = sig_Hz_reg/10;

end

endmodule

binbcd14.v

`timescale 1ns / 1ps

module binbcd14(

input wire [13:0]b,

output reg [16:0]p

);

reg [32:0]z;

integer i;

always@(*)

begin

for(i=0;i<=32;i=i+1)

z[i]=0;

z[16:3]=b;

repeat(11)

begin

if(z[17:14]>4)

z[17:14]=z[17:14]+3;

if(z[21:18]>4)

z[21:18]=z[21:18]+3;

if(z[25:22]>4)

z[25:22]=z[25:22]+3;

if(z[29:26]>4)

z[29:26]=z[29:26]+3;

z[32:1]=z[31:0];

end

p=z[30:14];

end

endmodule

x7segbc.v

`timescale 1ns / 1ps

module x7segbc(

input wire[15:0]x,

input wire cclk,

input wire clr,

output reg[6:0]a_to_g,

output reg[3:0]an

);

reg [1:0]s;

reg[3:0]digit;

wire [3:0]aen;

assign aen[3]=x[15]|x[14]|x[13]|x[12];

assign aen[2]=x[15]|x[14]|x[13]|x[12]|x[11]|x[10]|x[9]|x[8];

assign aen[1]=x[15]|x[14]|x[13]|x[12]|x[11]|x[10]|x[9]|x[8]|x[7]|x[6]|x[5]|x[4];

assign aen[0]=1;

always@(*)

case(s)

0:digit=x[3:0];

1:digit=x[7:4];

2:digit=x[11:8];

3:digit=x[15:12];

default:digit=x[3:0];

endcase

always@(*)

case(digit)

0:a_to_g = 7'b1111110;

1:a_to_g = 7'b0110000;

2:a_to_g = 7'b1101101;

3:a_to_g = 7'b1111001;

4:a_to_g = 7'b0110011;

5:a_to_g = 7'b1011011;

6:a_to_g = 7'b1011111;

7:a_to_g = 7'b1110000;

8:a_to_g = 7'b1111111;

9:a_to_g = 7'b1111011;

'hA:a_to_g = 7'b1110111;

'hB:a_to_g = 7'b0011111;

'hC:a_to_g = 7'b1001110;

'hD:a_to_g = 7'b0111101;

'hE:a_to_g = 7'b1001111;

'hF:a_to_g = 7'b1000111;

default :a_to_g =7'b1111110;

endcase

always@(*)

begin

an=4'b0000;

if(aen[s]==1)

an[s]=1;

end

always@(posedge cclk or posedge clr)

begin

if(clr==1)

s<=0;

else

s<=s+1;

end

endmodule

版权声明:本文为CSDN博主「李老狗在看FPGA」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/qq_37512669/article/details/90761742