1、使用规则

在rtl仿真中,x和z是两个情况,而在综合时被视为一种情况。因此在需要综合的代码中,是不允许出现x和z的。verilog使用规则如下:

① case 分支中不允许出现x、z、?

② 可以使用casez,但是不允许使用z和x

③ 禁止使用casex语句

2、case 分支中不允许出现x、z、?

case语句中出现“x”,“z”,“?”,容易导致综合前后不一致。

如下代码错误:

always@(posedge clk) begin case(sel) 1’b0: out =!in; 1’b1: out = in ; 1’bz: out = 1’b1; 1’bx: out = 1’b0; default: out = 1’b1 ; endcase end

3、可以使用casez语句,但是只能用“?”

使用casez语句和”?”配合,可以过滤不相关的比特位,但是casez语句中不能“x”和“z”

如下代码正确:“?”表示为0或者1

wire sel [2:0] ; always@(posedge clk) begin casez(sel) 3’b001: data_out <= data_in0 ; 3’b01?: data_out <= data_in1 ; 3’b1??: data_out <= data_in2 ; default : data_out <= 4’b0 ; end

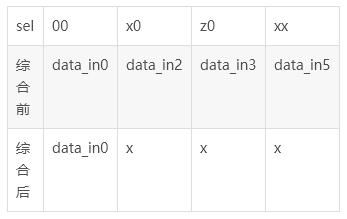

4、禁止使用casex语句

在可综合设计中,只能用case和casez,不能用casex,因为综合时casex中的x和z都被视为don’t care,综合前后仿真结果不一致。

casex(sel) 2’b00: data_out=data_in0 ; 2’b01: data_out=data_in1 ; 2’bx0: data_out=data_in2 ; 2’bz0: data_out=data_in3 ; 2’b1?: data_out=data_in4 ; default: data_out=data_in5 ;

综合前后结果如下:

版权声明:本文为CSDN博主「IC小鸽」的原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/icxiaoge/article/details/88853578