版权声明:本文为CSDN博主「Chenxr32」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/QDchenxr/article/details/120277813

用Vivado开发ZYNQ时,常用到Block Design。Block Design中不仅仅可以添加IP核,还可以将未封装成IP的.v或.vhd文件作为模块加入其中。我们以往Block Design中加一个闪灯的模块为例,说明如何向Block Design添加.v文件模块。

1、启动Vivado,创建一个工程,并创建一个Block Design和一个led.v文件。下面贴出led.v和约束文件的代码。

//led.v

`timescale 1ns / 1ps

module led

#(

parameter FREQ = 32'd49_999_999//这个参数可以在Block Design中修改

)

(

input sys_clk,

output reg [1:0] led

);

reg[31:0] timer_cnt;

always@(posedge sys_clk)

begin

if(timer_cnt >= FREQ)

begin

led <= ~led;

timer_cnt <= 32'd0;

end

else

begin

led <= led;

timer_cnt <= timer_cnt + 32'd1;

end

end

endmodule

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

set_property PACKAGE_PIN G14 [get_ports {led[1]}]

set_property PACKAGE_PIN M15 [get_ports {led[0]}]

set_property PACKAGE_PIN K17 [get_ports sys_clk]

create_clock -period 20.000 -name sys_clk -waveform {0.000 10.000} [get_ports sys_clk]

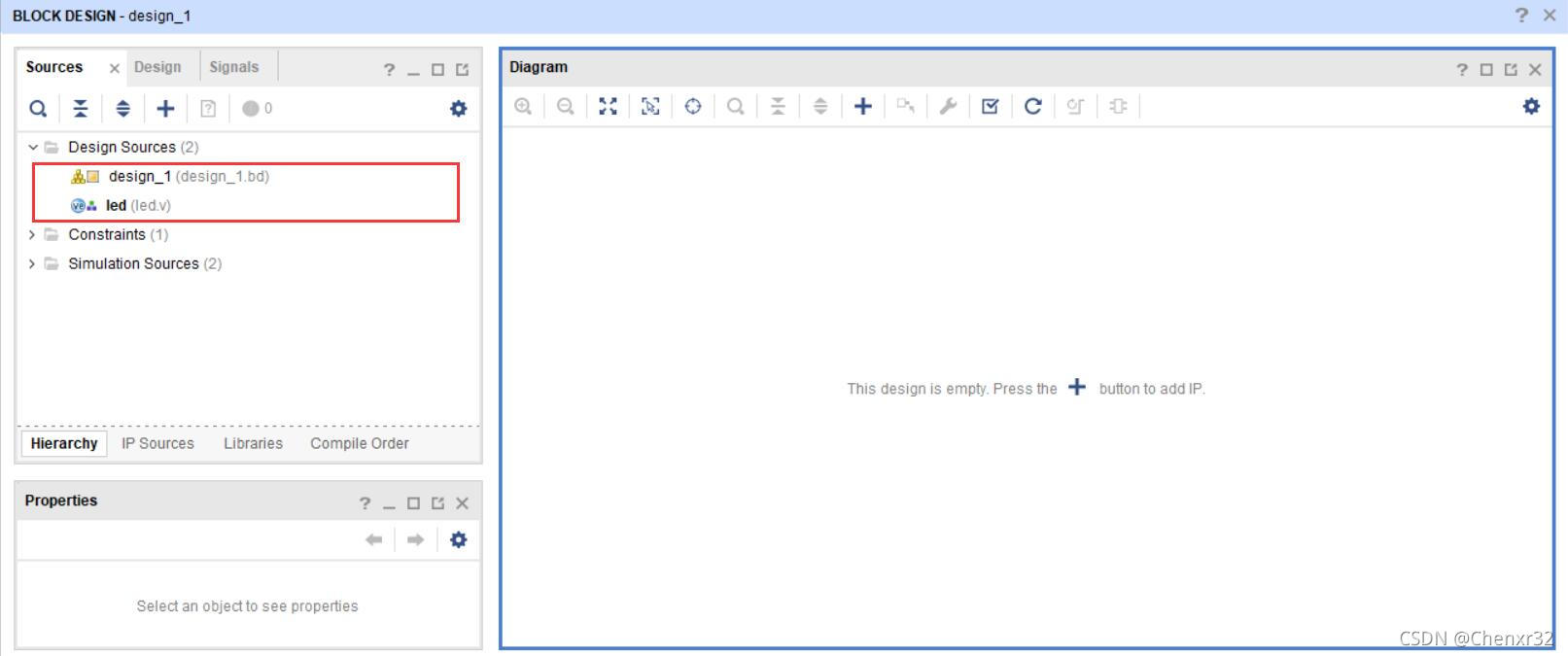

led.v还没添加入Block Design,这两个模块是平级的,如下图所示。

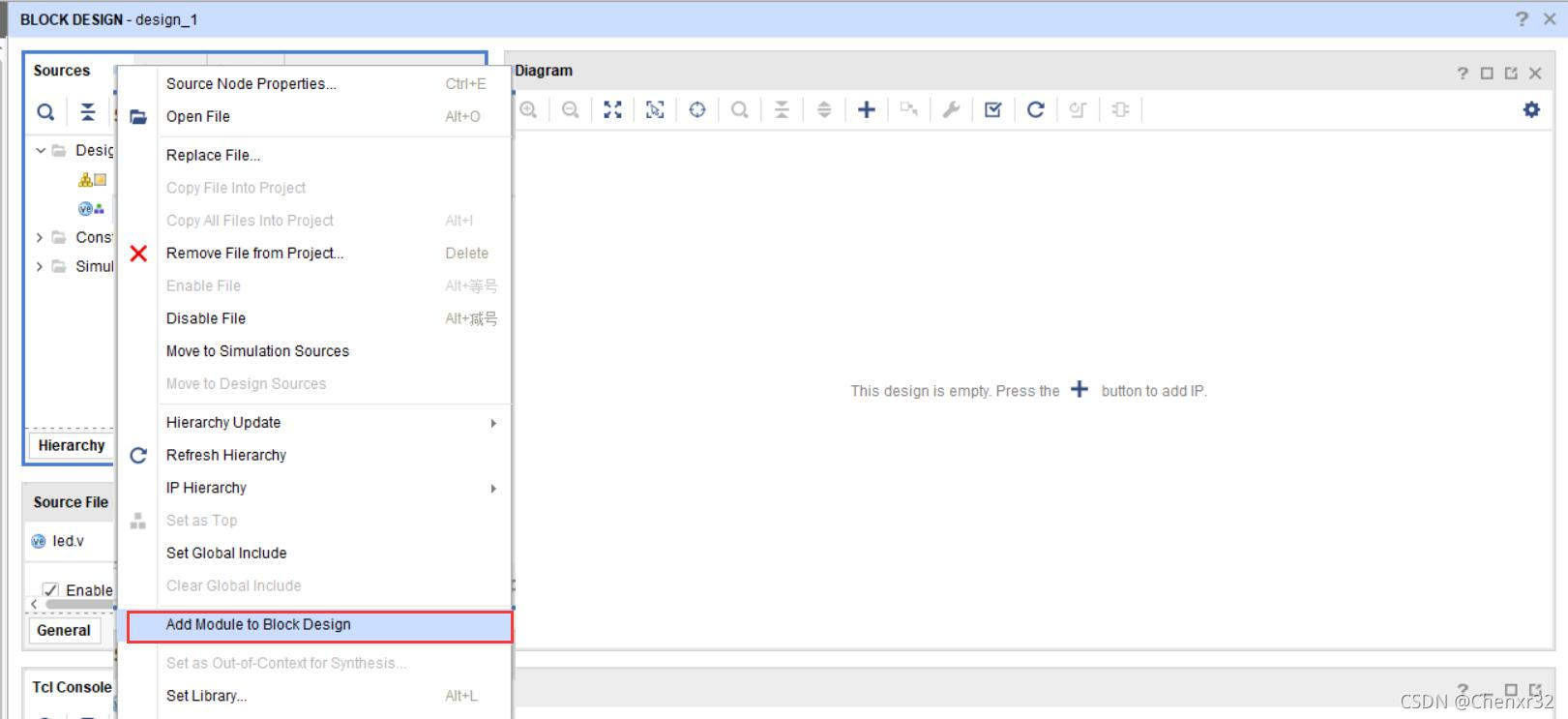

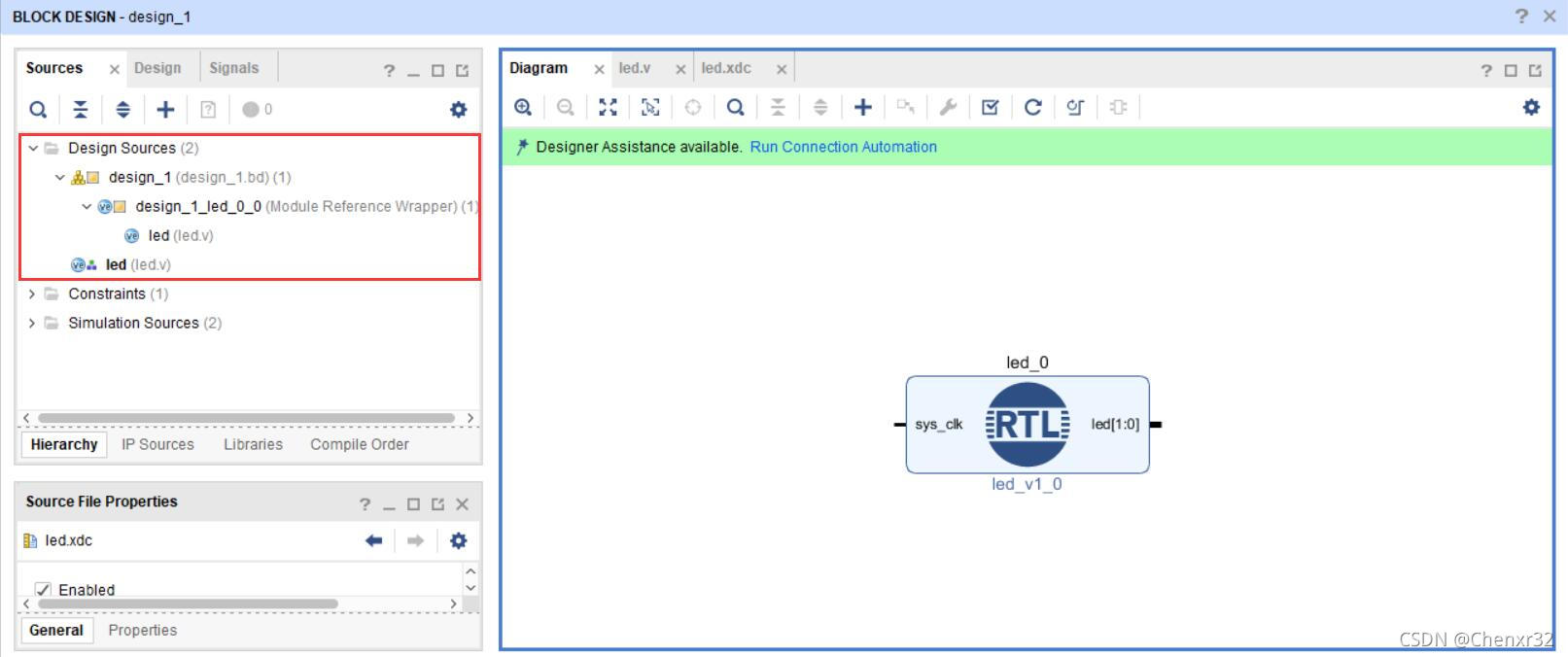

2、右键点击led.v,点击"Add Module to Block Design",将led.v作为模块加入到Block Design中。这时可以看到led.v和Block Design的层次关系。

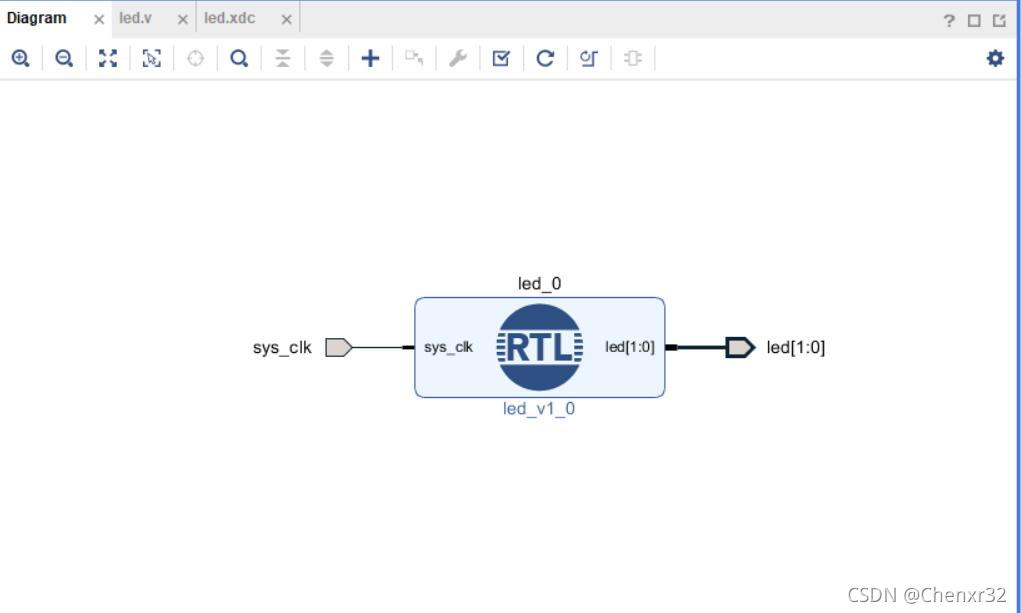

3、引出led_0模块的sys_clk和led[1:0]的引脚,方法是右击引脚点击“Make External”。然后给引出的引脚改名字,和约束文件中的引脚名称相同。

led.v的模块中有一个参数,这个参数的值可以双击led_0模块,然后修改,如下图所示。

4、执行Wrapper、Generate、分析、综合、实现、生成bitstream等操作。最后将bitstream下载进开发板看一下现象,两个灯以0.5Hz的频率闪烁。可以在Block Design中改一下FREQ参数的值,再看看LED闪烁的情况。

我这里的例子比较简单,复杂点儿的工程,比如有一个PS模块,也是可以这样向Block Design添加.v文件的。这种不封装IP,直接添加.v文件作为模块的方法可以比较灵活的修改还没有调试好的模块,等到所有bug都解决后再将.v文件封装成IP核。