本文转载自:十年老鸟的CSDN博客

前言

前面我们理解了TXOUTCLK和RXOUTCLK的源头,那TXOUTCLK/RXOUTCLK最终要输出做什么用呢。就是用来生成TXUSERCLK、TXUSERCLK2和RXUSERCLK、RXUSERCLK2的。

TXUSRCLK、TXUSRCLK2

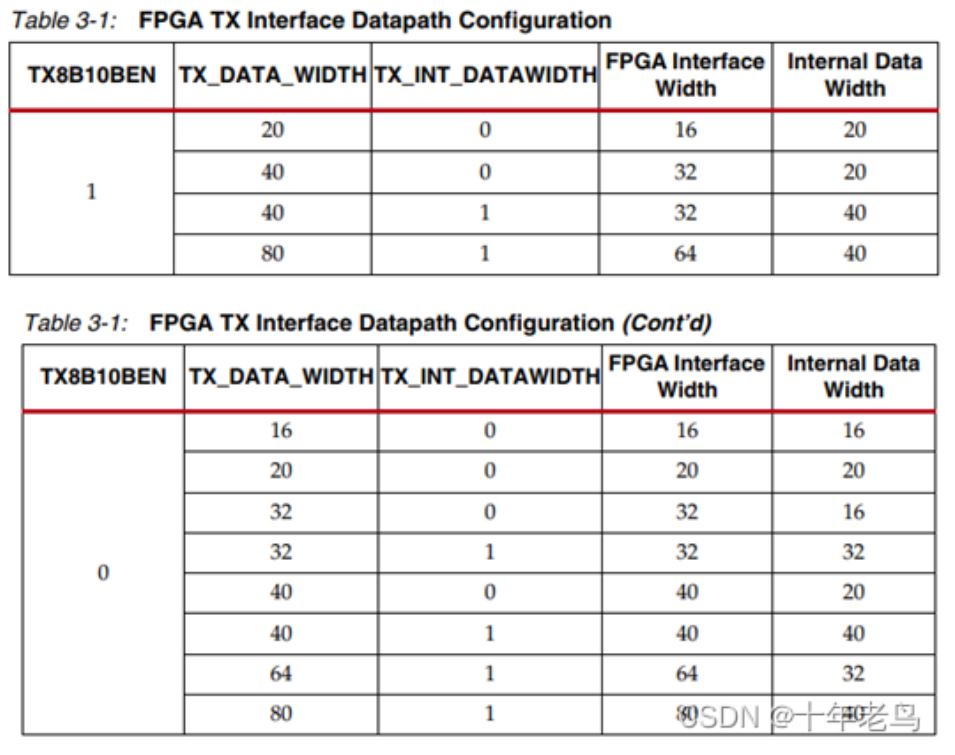

要理解TXUSERCLK、TXUSERCLK2的区别,从FPGA TX的接口开始,我们怎么将数据让transceiver发送出去呢:是用TXDATA端口,这个端口是处于TXUSERCLK2的时钟域下。这个端口的位宽是可以配置的,可以配成2、4、8字节宽。实际上的宽度是根据TX_DATA_WIDTH和TX_INT_DATAWIDTH

属性以及TX8B10BEN端口的设置来确定的。端口的宽度可以是16、20、32、40、64和80bit。接口上的并行时钟的速率(TXUSRCLK2)由TX线速率、TXDATA端口的宽度和是否是用8B/10B编码决定的。第二个并行时钟(TXUSRCLK)必须提供给发射器内部的PCS逻辑。

TX_INT_DATAWIDTH 是决定内部数据通道是2byte还是4byte。同时根据TX8B10BEN来确定这个

2byte的TX_INT_DATAWIDTH是16bit还是20bit;以及4byte的TX_INT_DATAWIDTH是32bit还是40bit。

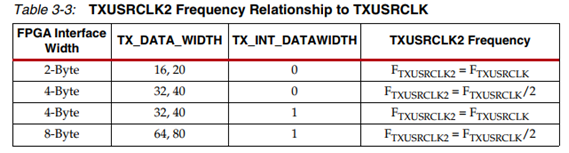

FPGA TX接口包含2个并行时钟: TXUSRCLK和TXUSRCLK2。TXUSRCLK是PCS逻辑的内部时钟。其时钟频率根据下面公式计算

TXUSRCLK2是所有进入TX测的主要的同步时钟。大部分进入TX测的信号都是在TXUSRCLK2时钟的上升沿采样。TXUSRCLK2和TXUSRCLK有固定的速率比关系取决于TX_DATA_WIDTH和TX_INT_DATAWIDTH这两个设定

这里出现了好多新的定义,

TX8B10BEN

TX_DATA_WIDTH

TX_INT_DATAWIDTH

FPGA Interface Width

Internal Data Width

TXUSRCLK2 Frequency

为了搞清楚前因后果,以及他们是影响TX链路的位宽变化的,我这里画一个图来进行加深理解

我想我已经写的很清楚了,不能在清楚了。

我们下面以2个例子来巩固下:JESD204B、JESD204C也都是基于SERDES来实现的

联想到我们之前是用的JESD204B CORE,它的配置是怎么样的。

首先我们知道FPGA InterfaceWidth = 32bit,而且JESD204B是有8B10B编码的,也就是TX8B10BEN = 1,那么TX_DATA_WIDTH = 40bit

TX_DATA_WIDTH = 40bit的时候TX_INT_DATAWIDTH可以是0或者1,如果是0,那么Internal Data Width = 20,当时我9.8304G的lane速率,那么TXUSRCLK = 491.52M. TXUSRCLK2 = 245.76M

那么Internal Data Width = 40,当时我9.8304G的lane速率,那么TXUSRCLK = 245.76M. TXUSRCLK2 = 245.76M

怎么感觉都可以。。理论上是都可以的

1、但JESD204B的协议规定了 Internal Data Width = 40了。所以TXUSRCLK = 245.76M. TXUSRCLK2 = 245.76M。

2、如果Internal Data Width = 20,TXUSRCLK = 491.52M. TXUSRCLK2 = 245.76M,那这里又得费MMCM的资源,完全没必要。且TXUSRCLK = 491.52M时序压力更大或者可能直接不支持。

那我们的JESD204C CORE或者10G光口,它的配置又是怎么样的呢

首先我们知道FPGA InterfaceWidth = 64bit,而且JESD204B是没有8B10B编码的,也就是TX8B10BEN = 0,那么TX_DATA_WIDTH = 64bit,没得选TX_INT_DATAWIDTH只能是1,Internal Data Width = 32。显然TXUSRCLK2 = TXUSRCLK/2。那这里就会耗费MMCM的资源了。所以我四个光口耗费了我5个MMCM,TX可共用耗费1个,RX耗费4个。求我心里的阴影面积

10.1376G的serdes接口,TXUSRCLK = 316.08M;TXUSRCLK = 158.4M 由此而来

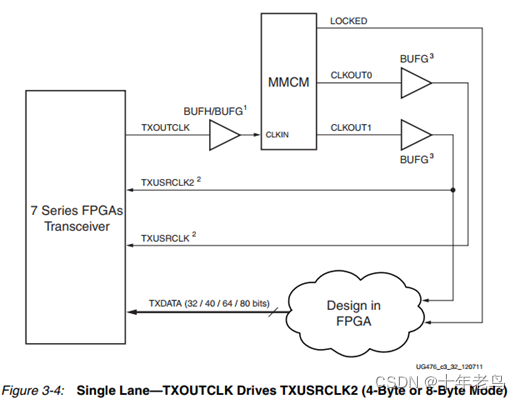

几种典型用法的框图

1、单条lane的 TXUSRCLK2 = TXUSRCLK

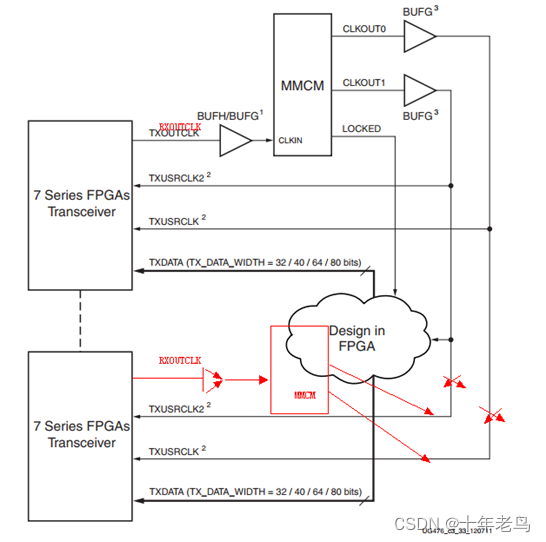

2、多条lane的 TXUSRCLK2 = TXUSRCLK

可以将一个transceiver作为主时钟源,分出来的TXUSRCLK和TXUSRCLK2可以给其他transceiver用

3、单条lane的 TXUSRCLK2 = TXUSRCLK/2

4、多条lane的 TXUSRCLK2 = TXUSRCLK/2

可以将一个transceiver作为主时钟源,经过一个MMCM,分出来的TXUSRCLK和TXUSRCLK2可以给其他transceiver用

RXUSRCLK、RXUSRCLK2

讲完了TXUSERCLK、TXUSERCLK2,那在讲讲RXUSERCLK、RXUSERCLK2。

几乎和TXUSERCLK、TXUSERCLK2一样。似乎没什么更多的说明

但有一点很关键(敲重点),就是多个lane的时候。因为我们的RXOUTCLK是使用serdes的恢复时钟。因此每条RX的lane必须使用自己独立的RXOUTCLK来生成各自的RXUSERCLK、RXUSERCLK2。这点再手册中居然不提示出来,真是有点LOW。