本文转载自: 硬码农二毛哥微信公众号

几年前FPGA时钟只需要连接一个单端输入的晶振,非常容易。现在不同了,差分时钟输入,差分信号又分为LVDS和LVPECL,时钟芯片输出后还要经过直流或交流耦合才能接入FPGA,有点晕了,今天仔细研究一下。

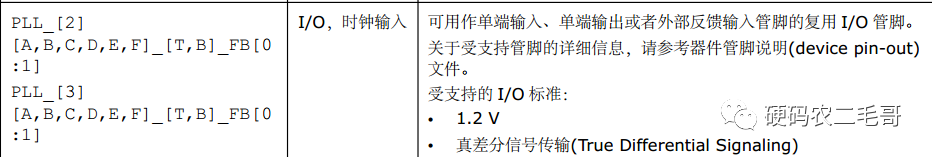

FPGA输入时钟要求

FPGA手册中对时钟输入的描述:

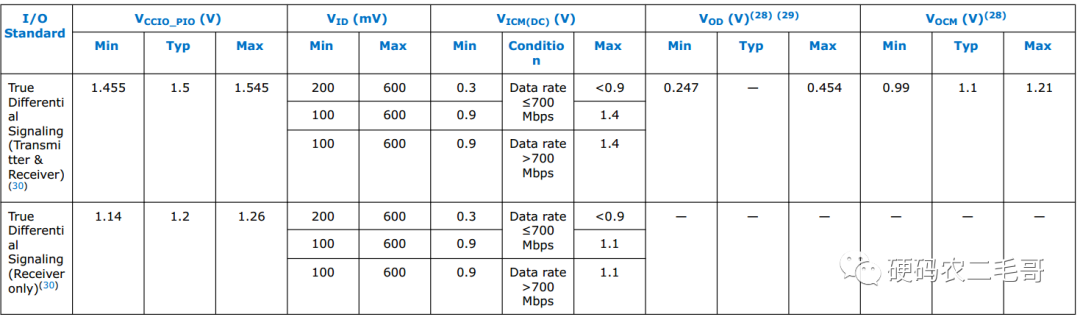

差分I/O电平标准:

真差分信号电压不能超过VICM(max) + VID(max)/2 。

直流耦合与交流耦合

时钟的发送端和接收端都有各自的电平接口类型,它们有可能不相同也可能是相同的。 这个时候通常就会有两种连接方式,即AC耦合以及DC耦合。 其实说简单也很简单,AC耦合就是中间用电容把发送接收端的共模电平隔开,而DC耦合就是不加电容。交流耦合(AC Coupling)就是通过隔直电容耦合,去掉了直流分量。直流耦合(DC Coupling)就是直通,交流直流一起过,并不是去掉了交流分量。

LVDS与LVPECL

时钟芯片输出时钟信号通常有LVDS和LVPECL。

当时时钟芯片输出LVDS信号时

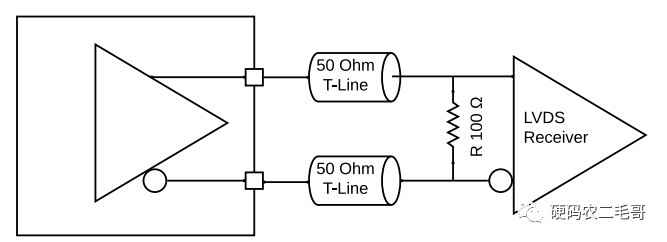

DC耦合

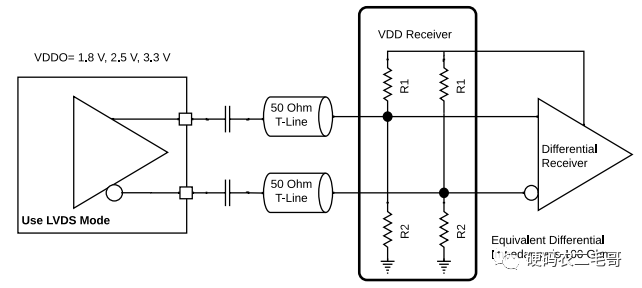

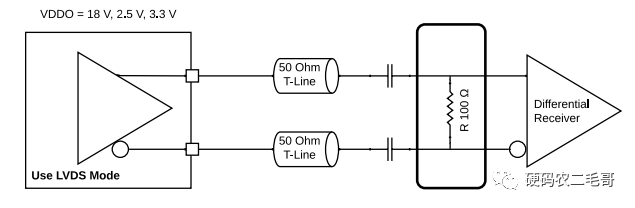

两种AC耦合方式。

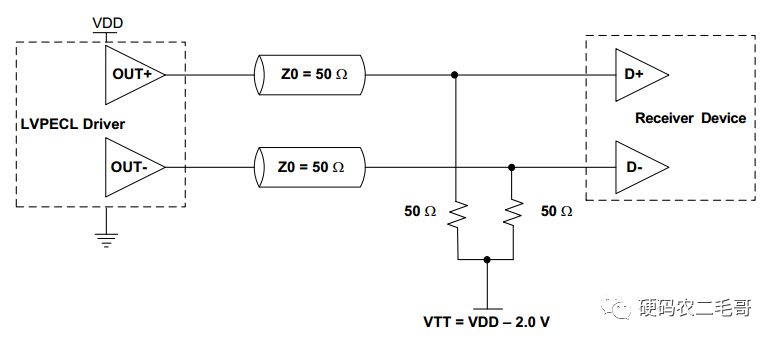

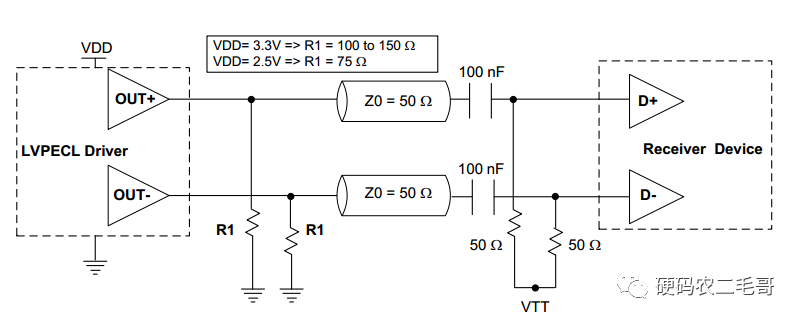

当时钟信号输出LVPECL信号时