本文转载自:OpenFPGA

使用 FPGA 播放音频(一)

这篇重点:如何从 SD 卡读取音频文件并将其输出到扬声器上。

开篇第一步

在上一篇教程中,创建了一个 I2S 发送器用来发送来从FPGA内部 ROM 的音频数据。下一步,我们向该 I2S 发送器添加 AXI-Stream 接口,这样我们就可以将发送器与 ZYNQ 的处理系统连接,还可以从 SD 卡读取音频数据。

为此,创建一个新的top设计。本设计应具有以下接口:

该块设计产生以下代码:

entity AXIS_I2S is

Generic ( RATIO : INTEGER := 8;

WIDTH : INTEGER := 16

);

Port ( MCLK : in STD_LOGIC;

nReset : in STD_LOGIC;

LRCLK : out STD_LOGIC;

SCLK : out STD_LOGIC;

SD : out STD_LOGIC;

ACLK : in STD_LOGIC;

ARESETn : in STD_LOGIC;

TDATA_RXD : in STD_LOGIC_VECTOR(31 downto 0);

TREADY_RXD : out STD_LOGIC;

TVALID_RXD : in STD_LOGIC

);

end AXIS_I2S;

SCLK与MCKL的比率通过RATIO参数定义,每个通道的数据字宽度通过WIDTH参数定义。

PS:此实现仅支持每个通道 16 位数据字(即立体声 32 位)。

设计中必须实现以下组件:

为分频器创建了一个过程,该过程在MCLK时钟上升沿对计数器进行计数,并在半个周期后切换信号SCLK_Int。

process

variable Counter : INTEGER := 0;

begin

wait until rising_edge(MCLK);

if(Counter < ((RATIO / 2) - 1)) then

Counter := Counter + 1;

else

Counter := 0;

SCLK_Int <= not SCLK_Int;

end if;

if(nReset = '0') then

Counter := 0;

SCLK_Int <= '0';

end if;

end process;

下一步是实现 AXI-Stream 接口。为此使用状态机:

process

begin

wait until rising_edge(ACLK);

case CurrentState is

when State_Reset =>

Tx_AXI <= (others => '0');

CurrentState <= State_WaitForTransmitterReady;

when State_WaitForTransmitterReady =>

if(Ready_AXI = '1') then

TREADY_RXD <= '1';

CurrentState <= State_WaitForValid;

else

TREADY_RXD <= '0';

CurrentState <= State_WaitForTransmitterReady;

end if;

when State_WaitForValid =>

if(TVALID_RXD = '1') then

TREADY_RXD <= '0';

Tx_AXI <= TDATA_RXD;

CurrentState <= State_WaitForTransmitterBusy;

else

TREADY_RXD <= '1';

CurrentState <= State_WaitForValid;

end if;

when State_WaitForTransmitterBusy =>

if(Ready_AXI = '0') then

CurrentState <= State_WaitForTransmitterReady;

else

CurrentState <= State_WaitForTransmitterBusy;

end if;

end case;

if(ARESETn = '0') then

CurrentState <= State_Reset;

end if;

end process;

复位后,机器从State_Reset状态变为State_WaitForTransmitter等待I2S 发送器发出就绪Ready信号的状态。一旦发送器准备好,TREADY_RXD就会设置 AXI-Stream 接口的信号,通知主机从机已准备好接收数据。然后从机改变为State_WaitForValid状态。

在此状态下,从机等待主机置位信号TVALID_RXD标记有效数据。一旦置位了信号,数据就会写入内部 FIFO。然后机器改变到State_WaitForTransmitterBusy状态。

现在状态机等待I2S发送器开始发送数据并“删除”就绪信号。一旦完成,状态机就会切换回State_WaitForTransmitterReady状态并再次等待,直到 I2S 发送器准备就绪。

这样,理论上 AXI-Stream 接口就完成了。不幸的是,最后变得有点棘手,因为当前的电路设计使用两个不同的时钟域:

一般来说,这两个时钟信号不能从时钟源生成(例如通过时钟分频器),因为 AXI 接口通常以 100 MHz 运行,而音频接口需要可以整齐地分频至采样频率的时钟速率,例如 12.288 MHz。因此,由于最差负裕量 (WNS) 和总负裕量 (TNS) 过多,在实现过程中会出现时序错误:

此外,由于触发器在不同时钟域中发生亚稳态而导致数据不正确的风险非常高。

因此,各个时钟域所使用的信号必须在每种情况下经由相应的电路传送到另一时钟域。Xilinx 在文档UG953(https://www.xilinx.com/support/documentation/sw_manuals/xilinx2018_3/ug9...)中描述了可用于此目的的相应宏。

宏的示例可以直接用于 VHDL 代码:

xpm_cdc_Data : xpm_cdc_handshake generic map ( DEST_EXT_HSK => 0,

DEST_SYNC_FF => 4,

INIT_SYNC_FF => 0,

SIM_ASSERT_CHK => 0,

SRC_SYNC_FF => 4,

WIDTH => (2 * WIDTH)

)

port map ( src_clk => ACLK,

src_in => Data_Fast,

dest_clk => MCLK,

dest_out => Data_Slow,

dest_ack => '0',

src_send => src_send,

src_rcv => src_rcv,

dest_req => dest_req

);

xpm_cdc_Ready : xpm_cdc_single generic map ( DEST_SYNC_FF => 4,

SRC_INPUT_REG => 1

)

port map ( src_clk => MCLK,

src_in => Ready_Transmitter,

dest_clk => ACLK,

dest_out => Ready_AXI

);

最后,必须插入 I2S 发送器并传递生成的信号。

Transmitter : I2S_Transmitter generic map ( WIDTH => WIDTH

)

port map( Clock => SCLK_Int,

nReset => nReset,

Ready => Ready_Transmitter,

Tx => Tx_Transmitter,

LRCLK => LRCLK,

SCLK => SCLK,

SD => SD

);

I2S 发送器的 AXI-Stream 接口现已准备就绪并可供使用。完整的代码如下所示:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

library xpm;

use xpm.vcomponents.all;

entity AXIS_I2S is

Generic ( RATIO : INTEGER := 8;

WIDTH : INTEGER := 16

);

Port ( MCLK : in STD_LOGIC;

nReset : in STD_LOGIC;

LRCLK : out STD_LOGIC;

SCLK : out STD_LOGIC;

SD : out STD_LOGIC;

ACLK : in STD_LOGIC;

ARESETn : in STD_LOGIC;

TDATA_RXD : in STD_LOGIC_VECTOR(31 downto 0);

TREADY_RXD : out STD_LOGIC;

TVALID_RXD : in STD_LOGIC

);

end AXIS_I2S;

architecture AXIS_I2S_Arch of AXIS_I2S is

type AXIS_State_t is (State_Reset, State_WaitForTransmitterReady, State_WaitForValid, State_WaitForTransmitterBusy);

signal CurrentState : AXIS_State_t := State_Reset;

signal Tx_AXI : STD_LOGIC_VECTOR(((2 * WIDTH) - 1) downto 0) := (others => '0');

signal Ready_AXI : STD_LOGIC;

signal Tx_Transmitter : STD_LOGIC_VECTOR(((2 * WIDTH) - 1) downto 0) := (others => '0');

signal Ready_Transmitter : STD_LOGIC;

signal SCLK_Int : STD_LOGIC := '0';

component I2S_Transmitter is

Generic ( WIDTH : INTEGER := 16

);

Port ( Clock : in STD_LOGIC;

nReset : in STD_LOGIC;

Ready : out STD_LOGIC;

Tx : in STD_LOGIC_VECTOR(((2 * WIDTH) - 1) downto 0);

LRCLK : out STD_LOGIC;

SCLK : out STD_LOGIC;

SD : out STD_LOGIC

);

end component;

begin

Transmitter : I2S_Transmitter generic map ( WIDTH => WIDTH

)

port map( Clock => SCLK_Int,

nReset => nReset,

Ready => Ready_Transmitter,

Tx => Tx_Transmitter,

LRCLK => LRCLK,

SCLK => SCLK,

SD => SD

);

xpm_cdc_Data : xpm_cdc_gray generic map ( DEST_SYNC_FF => 4,

SIM_ASSERT_CHK => 0,

SIM_LOSSLESS_GRAY_CHK => 0,

WIDTH => (2 * WIDTH)

)

port map ( src_clk => ACLK,

src_in_bin => Tx_AXI,

dest_clk => MCLK,

dest_out_bin => Tx_Transmitter

);

xpm_cdc_Ready : xpm_cdc_single generic map ( DEST_SYNC_FF => 4,

SRC_INPUT_REG => 1

)

port map ( src_clk => MCLK,

src_in => Ready_Transmitter,

dest_clk => ACLK,

dest_out => Ready_AXI

);

process

variable Counter : INTEGER := 0;

begin

wait until rising_edge(MCLK);

if(Counter < ((RATIO / 2) - 1)) then

Counter := Counter + 1;

else

Counter := 0;

SCLK_Int <= not SCLK_Int;

end if;

if(nReset = '0') then

Counter := 0;

SCLK_Int <= '0';

end if;

end process;

process

begin

wait until rising_edge(ACLK);

case CurrentState is

when State_Reset =>

Tx_AXI <= (others => '0');

CurrentState <= State_WaitForTransmitterReady;

when State_WaitForTransmitterReady =>

if(Ready_AXI = '1') then

TREADY_RXD <= '1';

CurrentState <= State_WaitForValid;

else

TREADY_RXD <= '0';

CurrentState <= State_WaitForTransmitterReady;

end if;

when State_WaitForValid =>

if(TVALID_RXD = '1') then

TREADY_RXD <= '0';

Tx_AXI <= TDATA_RXD;

CurrentState <= State_WaitForTransmitterBusy;

else

TREADY_RXD <= '1';

CurrentState <= State_WaitForValid;

end if;

when State_WaitForTransmitterBusy =>

if(Ready_AXI = '0') then

CurrentState <= State_WaitForTransmitterReady;

else

CurrentState <= State_WaitForTransmitterBusy;

end if;

end case;

if(ARESETn = '0') then

CurrentState <= State_Reset;

end if;

end process;

end AXIS_I2S_Arch;

接下来,我们希望使用该接口从 SD 卡读取波形文件,并使用 CS4344 D/A 转换器通过连接的扬声器输出音乐。

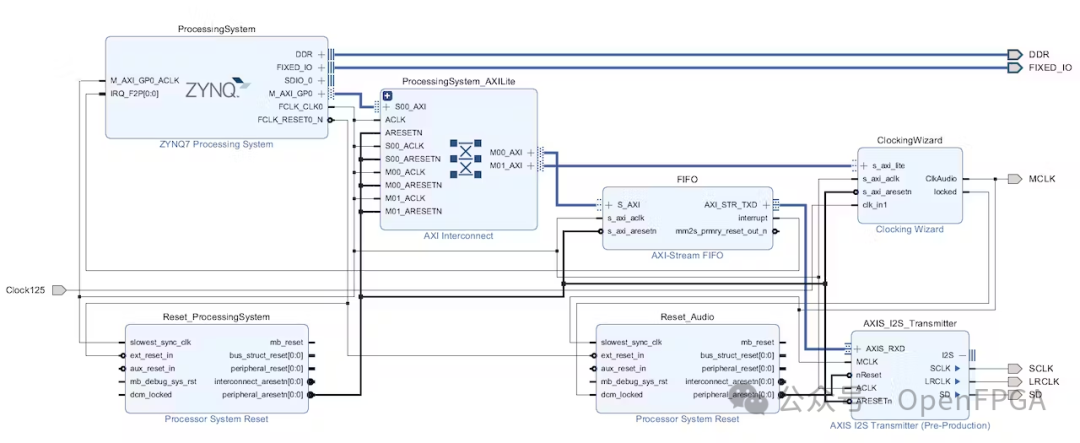

该项目需要以下IP核:

时钟向导生成时钟,然后将其用作 CS4344 的主时钟。输出时钟可以通过 AXI-Lite 接口适应音频文件的采样率。

AXI-Stream FIFO 充当处理系统和 I2S 发送器之间的链接。处理系统通过 AXI-Lite(或 AXI)接口将数据写入 FIFO,然后将数据传输至 I2S 发送器。

根据设计创建比特流,然后可以开发软件。

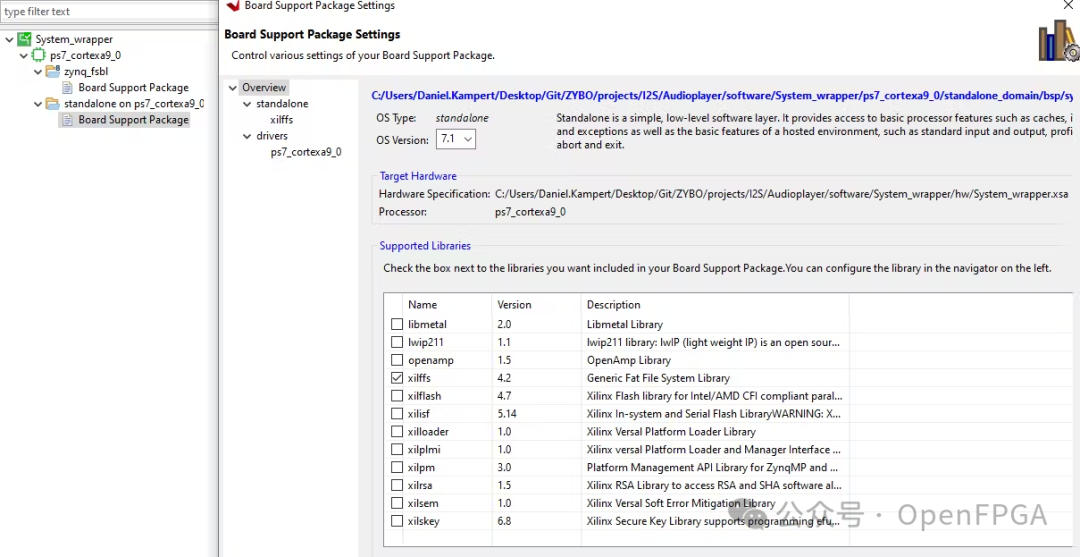

读取 SD 卡需要 Xilinx 的 xilffs FAT 库,该库必须集成到 Vitis 项目的板级支持包中(不要忘记启用LFN支持大文件名的选项):

第一步,软件使用该AudioPlayer_Init函数初始化音频播放器,从而初始化 FIFO、GIC 和中断处理程序,以及时钟向导和 SD 卡。

u32 AudioPlayer_Init(void)

{

xil_printf("[INFO] Looking for FIFO configuration...\r\n");

_Fifo_ConfigPtr = XLlFfio_LookupConfig(XPAR_FIFO_DEVICE_ID);

if(_Fifo_ConfigPtr == NULL)

{

xil_printf("[ERROR] Invalid FIFO configuration!\r\n");

return XST_FAILURE;

}

xil_printf("[INFO] Initialize FIFO...\r\n");

if(XLlFifo_CfgInitialize(&_Fifo, _Fifo_ConfigPtr, _Fifo_ConfigPtr->BaseAddress) != XST_SUCCESS)

{

xil_printf("[ERROR] FIFO initialization failed!\n\r");

return XST_FAILURE;

}

xil_printf("[INFO] Looking for GIC configuration...\r\n");

_GIC_ConfigPtr = XScuGic_LookupConfig(XPAR_PS7_SCUGIC_0_DEVICE_ID);

if(_GIC_ConfigPtr == NULL)

{

xil_printf("[ERROR] Invalid GIC configuration!\n\r");

return XST_FAILURE;

}

xil_printf("[INFO] Initialize GIC...\r\n");

if(XScuGic_CfgInitialize(&_GIC, _GIC_ConfigPtr, _GIC_ConfigPtr->CpuBaseAddress) != XST_SUCCESS)

{

xil_printf("[ERROR] GIC initialization failed!\n\r");

return XST_FAILURE;

}

xil_printf("[INFO] Setup interrupt handler...\r\n");

XScuGic_SetPriorityTriggerType(&_GIC, XPAR_FABRIC_FIFO_INTERRUPT_INTR, 0xA0, 0x03);

if(XScuGic_Connect(&_GIC, XPAR_FABRIC_FIFO_INTERRUPT_INTR, (Xil_ExceptionHandler)AudioPlayer_FifoHandler, &_Fifo) != XST_SUCCESS)

{

xil_printf("[ERROR] Can not connect interrupt handler!\n\r");

return XST_FAILURE;

}

XScuGic_Enable(&_GIC, XPAR_FABRIC_FIFO_INTERRUPT_INTR);

xil_printf("[INFO] Enable exceptions...\r\n");

Xil_ExceptionInit();

Xil_ExceptionRegisterHandler(XIL_EXCEPTION_ID_INT, (Xil_ExceptionHandler)XScuGic_InterruptHandler, &_GIC);

Xil_ExceptionEnable();

xil_printf("[INFO] Enable FIFO interrupts...\r\n");

XLlFifo_IntClear(&_Fifo, XLLF_INT_ALL_MASK);

xil_printf("[INFO] Initialize Clocking Wizard...\r\n");

if((ClockingWizard_Init(&_ClkWiz, XPAR_CLOCKINGWIZARD_BASEADDR) || ClockingWizard_GetOutput(&_ClkWiz, &_AudioClock))!= XST_SUCCESS)

{

xil_printf("[ERROR] Clocking Wizard initialization failed!\n\r");

return XST_FAILURE;

}

xil_printf("[INFO] Mount SD card...\r\n");

if(SD_Init())

{

xil_printf("[ERROR] Can not initialize SD card!\n\r");

return XST_FAILURE;

}

return XST_SUCCESS;

}

一旦初始化完成,就会调用AudioPlayer_LoadFile函数从 SD 卡加载Audio.wav文件 。

if(AudioPlayer_LoadFile("Audio.wav"))

{

xil_printf("[ERROR] Can not open Audio file!\n\r");

return XST_FAILURE;

}

u32 AudioPlayer_LoadFile(char* File)

{

if(SD_LoadFileFromCard(File, &_File))

{

xil_printf("[ERROR] Can not open Audio file!\n\r");

return XST_FAILURE;

}

xil_printf(" File size: %lu bytes\n\r", _File.Header.ChunkSize + 8);

xil_printf(" File format: %lu\n\r", _File.Format.AudioFormat);

xil_printf(" Channels: %lu\n\r", _File.Format.NumChannels);

xil_printf(" Sample rate: %lu Hz\n\r", _File.Format.SampleRate);

xil_printf(" Bits per sample: %lu bits\n\r", _File.Format.BitsPerSample);

xil_printf(" Block align: %lu bytes\n\r", _File.Format.BlockAlign);

xil_printf(" Data bytes: %lu bytes\n\r", _File.Header.ChunkSize / _File.Format.NumChannels);

xil_printf(" Samples: %lu\n\r", 8 * _File.Header.ChunkSize / _File.Format.NumChannels / _File.Format.BitsPerSample);

if(( _File.Format.BitsPerSample != 16) || (_File.Format.NumChannels > 2))

{

xil_printf("[ERROR] Invalid file format!\n\r");

return XST_FAILURE;

}

AudioPlayer_ChangeFreq(_File.Format.SampleRate);

XLlFifo_TxReset(&_Fifo);

XLlFifo_IntEnable(&_Fifo, XLLF_INT_ALL_MASK);

SD_CopyDataIntoBuffer(_FifoBuffer, 256);

AudioPlayer_CopyBuffer();

return XST_SUCCESS;

}

该函数AudioPlayer_LoadFile调用函数SD_LoadFileFromCard从SD卡加载波形文件。

u32 SD_LoadFileFromCard(const char* FileName, Wave_t* File)

{

xil_printf("[INFO] Opening file: %s...\n\r", FileName);

if(f_open(&_FileHandle, FileName, FA_READ))

{

xil_printf("[ERROR] Can not open audio file!\n\r");

return XST_FAILURE;

}

if(f_read(&_FileHandle, &File->RIFF, sizeof(Wave_RIFF_t), &_BytesRead) || f_read(&_FileHandle, &File->Format, sizeof(Wave_Format_t), &_BytesRead))

{

xil_printf("[ERROR] Can not read SD card!\n\r");

return XST_FAILURE;

}

Wave_Header_t Header;

uint32_t Offset = sizeof(Wave_RIFF_t) + sizeof(Wave_Format_t);

if(f_read(&_FileHandle, Header.ChunkID, sizeof(Wave_Header_t), &_BytesRead) || f_lseek(&_FileHandle, Offset))

{

xil_printf("[ERROR] Can not read SD card!\n\r");

return XST_FAILURE;

}

if(strncmp("LIST", Header.ChunkID, 4) == 0)

{

Offset += Header.ChunkSize + sizeof(Wave_Header_t);

if(f_read(&_FileHandle, &File->ListHeader, sizeof(Wave_Header_t), &_BytesRead) || f_lseek(&_FileHandle, Offset))

{

xil_printf("[ERROR] Can not place SD card pointer!\n\r");

return XST_FAILURE;

}

}

if(f_read(&_FileHandle, &File->DataHeader, sizeof(Wave_Header_t), &_BytesRead))

{

xil_printf("[ERROR] Can not read SD card!\n\r");

return XST_FAILURE;

}

if(File->Format.AudioFormat != WAVE_FORMAT_PCM)

{

xil_printf("[ERROR] Audio format not supported! Keep sure that the file use the PCM format!\n\r");

return XST_FAILURE;

}

_RemainingBytes = File->DataHeader.ChunkSize;

_IsBusy = true;

return XST_SUCCESS;

}

在下一步中,根据使用的采样频率从波形文件中设置时钟向导的输出频率:

static void AudioPlayer_ChangeFreq(const u32 SampleRate)

{

if(SampleRate == 44100)

{

xil_printf(" Use clock setting 1...\n\r");

_ClkWiz.DIVCLK_DIVIDE = 5;

_ClkWiz.CLKFBOUT_MULT = 42;

_ClkWiz.CLKFBOUT_Frac_Multiply = 0;

_AudioClock.DIVIDE = 93;

_AudioClock.FRAC_Divide = 0;

}

else if(SampleRate == 48000)

{

xil_printf(" Use clock setting 2...\n\r");

_ClkWiz.DIVCLK_DIVIDE = 3;

_ClkWiz.CLKFBOUT_MULT = 23;

_ClkWiz.CLKFBOUT_Frac_Multiply = 0;

_AudioClock.DIVIDE = 78;

_AudioClock.FRAC_Divide = 0;

}

else if(SampleRate == 96000)

{

xil_printf(" Use clock setting 3...\n\r");

_ClkWiz.DIVCLK_DIVIDE = 3;

_ClkWiz.CLKFBOUT_MULT = 23;

_ClkWiz.CLKFBOUT_Frac_Multiply = 0;

_AudioClock.DIVIDE = 39;

_AudioClock.FRAC_Divide = 0;

}

ClockingWizard_SetClockBuffer(&_ClkWiz);

ClockingWizard_SetOutput(&_ClkWiz, &_AudioClock);

}

加载音频文件并且调整时钟向导的输出频率后,将从波形文件中读取第一个数据块并将其复制到 FIFO:

u32 SD_CopyDataIntoBuffer(u8* Buffer, const u32 Length)

{

if(_RemainingBytes >= Length)

{

if(f_read(&_FileHandle, Buffer, Length, &_BytesRead))

{

return XST_FAILURE;

}

_RemainingBytes -= _BytesRead;

}

else

{

if(f_read(&_FileHandle, Buffer, _RemainingBytes, &_BytesRead))

{

return XST_FAILURE;

}

if(f_close(&_FileHandle))

{

xil_printf("[ERROR] Can not close audio file!\n\r");

return XST_FAILURE;

}

_IsBusy = false;

}

return XST_SUCCESS;

}

程序流程的其余部分在 FIFO 的回调中进行:

static void AudioPlayer_FifoHandler(void* CallbackRef)

{

XLlFifo* InstancePtr = (XLlFifo*)CallbackRef;

u32 Pending = XLlFifo_IntPending(InstancePtr);

while(Pending)

{

if(Pending & XLLF_INT_TC_MASK)

{

SD_CopyDataIntoBuffer(_FifoBuffer, AUDIOPLAYER_FIFO_BUFFER_SIZE);

XLlFifo_IntClear(InstancePtr, XLLF_INT_TC_MASK);

}

else if(Pending & XLLF_INT_TFPE_MASK)

{

AudioPlayer_CopyBuffer();

if(!SD_IsBusy())

{

XLlFifo_IntDisable(&_Fifo, XLLF_INT_ALL_MASK);

}

XLlFifo_IntClear(InstancePtr, XLLF_INT_TFPE_MASK);

}

else if(Pending & XLLF_INT_ERROR_MASK)

{

xil_printf(" Error: %lu!\n\r", Pending);

XLlFifo_IntClear(InstancePtr, XLLF_INT_ERROR_MASK);

}

else

{

XLlFifo_IntClear(InstancePtr, Pending);

}

Pending = XLlFifo_IntPending(InstancePtr);

}

}

一旦 FIFO 触发TFPE中断(发送 FIFO 可编程空),FIFO 就会被来自内部缓冲区的新数据填充。当从处理系统到 FIFO 的传输完成时,会触发TC中断(传输完成),并从 SD 卡读取下一个数据块。之后重复进行上面步骤,直到文件完全播放。

static void AudioPlayer_CopyBuffer(void)

{

u32 Bytes = 0x00;

for(u32 i = 0x00; i < AUDIOPLAYER_FIFO_BUFFER_SIZE; i += _File.Format.BlockAlign)

{

u32 Word = 0x00;

for(u8 Byte = 0x00; Byte < _File.Format.BlockAlign; Byte++)

{

Word |= _FifoBuffer[i + Byte];

Word <<= 0x08;

}

if(XLlFifo_iTxVacancy(&_Fifo))

{

XLlFifo_TxPutWord(&_Fifo, Word);

Bytes += sizeof(u32);

}

}

XLlFifo_iTxSetLen(&_Fifo, Bytes);

}

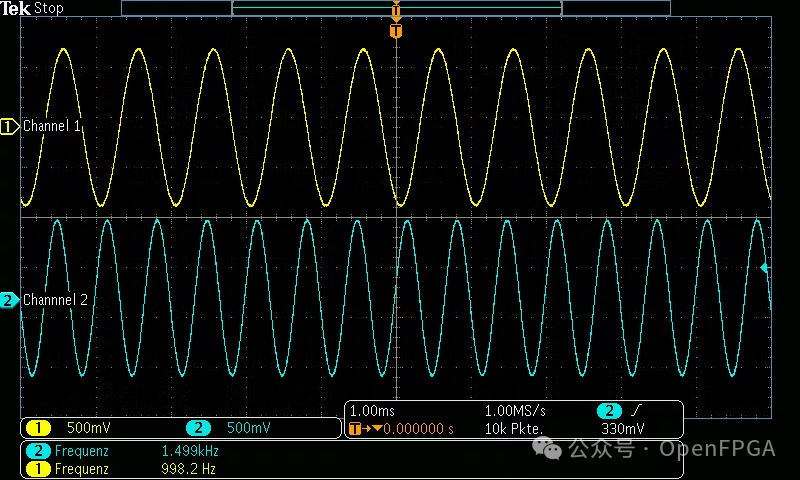

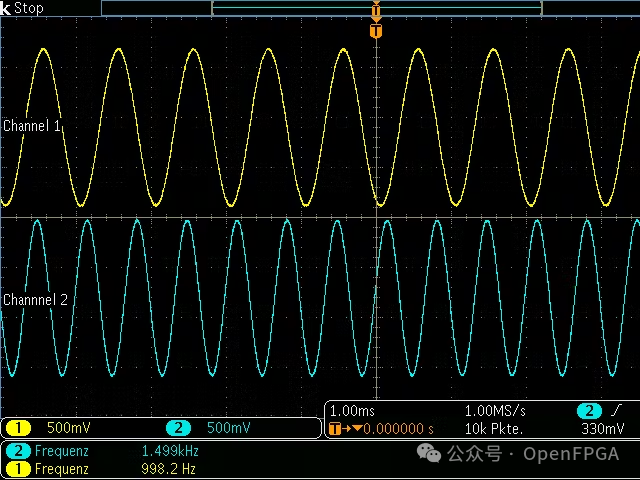

现在需要一个波形文件。简单的测试信号可以wavtones.com上生成(https://www.wavtones.com/functiongenerator.php)。

然后,只需将相应的文件以Audio.wav名称复制到 SD 卡上,即可开始使用。

-----------I2S Audio player-----------

[INFO] Looking for FIFO configuration...

[INFO] Initialize FIFO...

[INFO] Looking for GIC configuration...

[INFO] Initialize GIC...

[INFO] Setup interrupt handler...

[INFO] Enable exceptions...

[INFO] Enable FIFO interrupts...

[INFO] Initialize Clocking Wizard...

[INFO] Mount SD card...

[INFO] Opening file: Single.wav...

File size: 264610 bytes

File format: 1

Channels: 1

Sample rate: 48000 Hz

Bits per sample: 16 bits

Data bytes: 264602 bytes

Samples: 132301

Use clock setting 2...

[INFO] Finished!

或者使用立体声音频:

-----------I2S Audio player-----------

[INFO] Looking for FIFO configuration...

[INFO] Initialize FIFO...

[INFO] Looking for GIC configuration...

[INFO] Initialize GIC...

[INFO] Setup interrupt handler...

[INFO] Enable exceptions...

[INFO] Enable FIFO interrupts...

[INFO] Initialize Clocking Wizard...

[INFO] Mount SD card...

[INFO] Opening file: Dual.wav...

File size: 529208 bytes

File format: 1

Channels: 2

Sample rate: 44100 Hz

Bits per sample: 16 bits

Block align: 4 bytes

Data bytes: 264600 bytes

Samples: 132300

Use clock setting 1...

[INFO] Finished!