作者:张海军 来源:傅里叶的猫

我们以一个简单的加法器为例,来看下如何用vcs+verdi仿真Verilog文件并查看波形。

源文件内容如下:

//adder.v module adder( input clk, input rst, input [9:0] A, input [9:0] B, output reg [10:0] C ); always @ ( posedge clk ) begin if(rst) C <= #`FFD 'b0; else C <= #`FFD A + B; end endmodule

我们再定义一个宏定义的文件:

//macro_define.sv `define FFD 1ns

我们需要再定义一个testbench文件:

//test.sv

module test;

reg clk;

reg rst;

reg [9:0] A;

reg [9:0] B;

wire [10:0] C;

initial begin

rst = 1;

A = 0;

B = 0;

#1us;

rst = 0;

#1us;

A = 10'd100;

B = 10'd200;

#1us;

A = 10'd300;

B = 10'd400;

#20us;

$finish;

end

initial begin

clk = 0;

forever #10ns clk <= ~clk;

end

adder add_inst(

.clk(clk),

.rst(rst),

.A(A),

.B(B),

.C(C)

);

`ifdef DUMP_FSDB

initial begin

$fsdbDumpfile("tb.fsdb");

$fsdbDumpvars("+all");

//string testname;

//if($value$plusargs("TESTNAME=%s", testname)) begin

// $fsdbDumpfile({testname, "_sim_dir/", testname, ".fsdb"});

//end else begin

// $fsdbDumpfile("tb.fsdb");

//end

end

`endif

endmodule再定义一个filelist文件:dut.f

./macro_define.sv ./adder.v ./test.sv

最后就是需要一个Makefile文件了:

#!/bin/make all: comp sim comp: vcs -full64 -timescale=1ns/1ps -V -R -sverilog \ -debug_access+all +vc +v2k -kdb \ -l vcs.log \ -f dut.f +define+DUMP_FSDB=1 \ -top test sim: ./simv -l simv.log clean: rm -rf *~ core csrc simv* vc_hdrs.h ucli.key urg* *.log novas.* *.fsdb* verdiLog 64* DVEfiles *.vpd

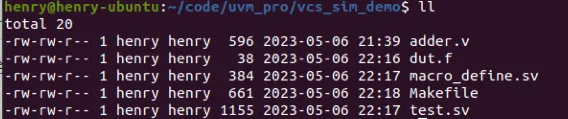

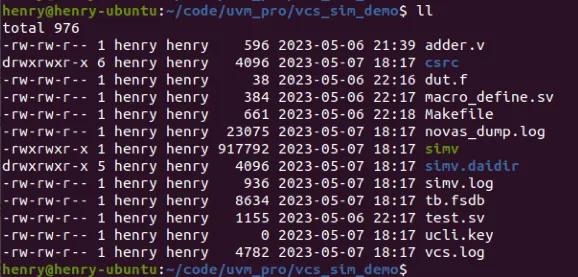

总的文件如下:

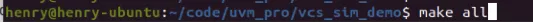

执行make all:

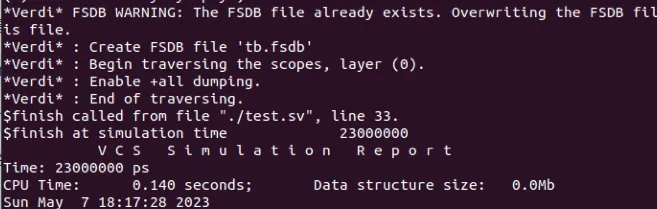

跑完后如下:

生成的文件如下:

用verdi打开波形:verdi -ssf tb.fsdb

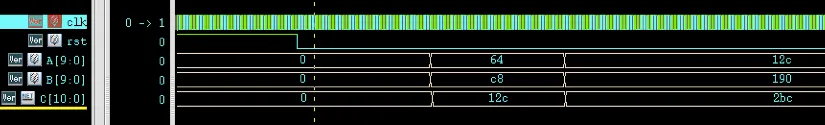

可以看到波形如下: