来源:FPGA入门到精通

在数字设计领域,时钟信号如同心跳一般,驱动着整个系统的节奏。FPGA设计中,时钟管理是确保系统同步和性能的基石。

本文将详细介绍FPGA时钟设计的概念、技巧和优化策略。

一、时钟源的分类与特性

时钟源根据其在数字设计中的位置,可分为外部时钟源和内部时钟源。

外部时钟源如RC/LC振荡电路和晶体振荡器。

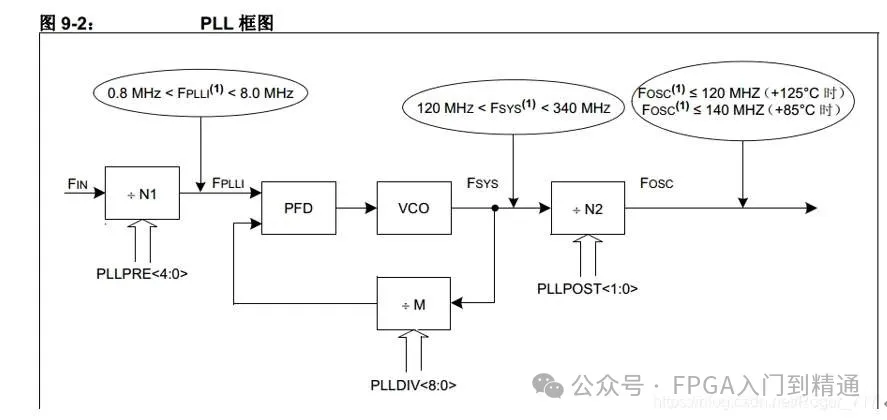

内部时钟源如PLL,它们通过外部参考信号实现输出信号频率的自动跟踪和倍频。

二、时钟特性的深入理解

时钟信号在实际电路中的传输和翻转并非理想化,存在时钟偏移、抖动、转换时间和延时等问题。

这些问题会影响时序的准确性和系统的性能。

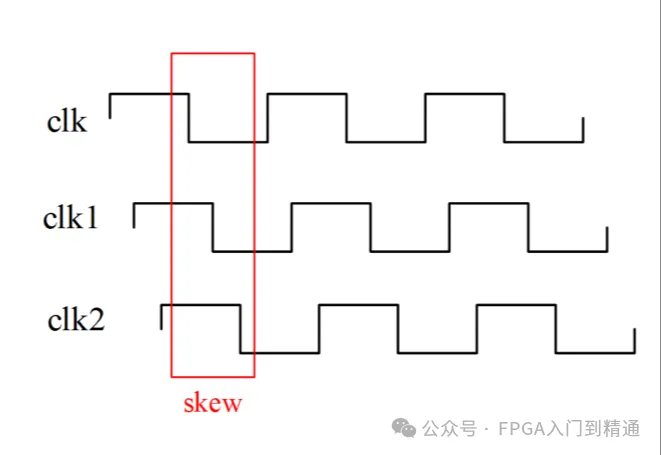

1、时钟偏移(Skew)

由线网延迟导致,不同触发器端口的时钟相位存在差异。

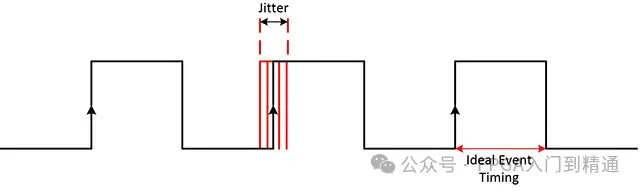

2、时钟抖动(Jitter)

实际时钟沿存在的不定时的偏移,分为随机抖动和固定抖动。

3、转换时间(Transition)

时钟电平跳变所需的过渡时间。

4、时钟延时(Latency)

时钟信号从源到触发器端口的传输延迟。

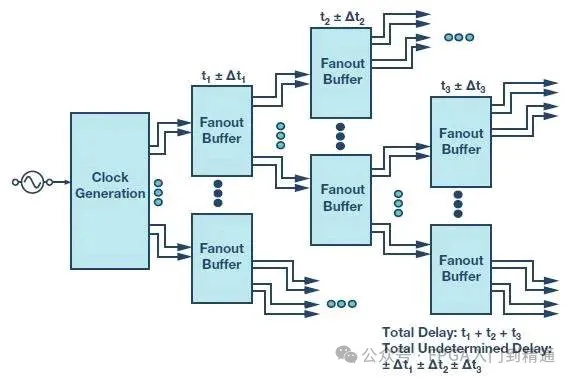

三、时钟树的构建与管理

时钟树是解决时钟延迟和驱动问题的关键结构,由多个缓冲单元平衡搭建,减少触发器之间的时间差异,确保时序和驱动能力。

四、同步与异步时钟的理解

同步时钟意味着所有触发器共享同一时钟信号,而异步时钟则可能存在多个独立时钟源。

同步电路中,触发器状态仅在时钟脉冲到来时改变。

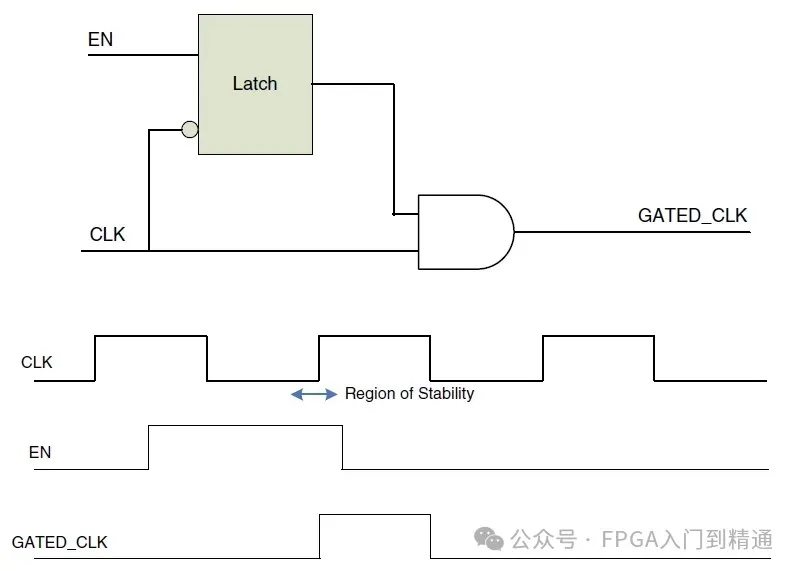

五、门控时钟的应用

门控时钟通过使能信号控制时钟的传递,有效降低功耗,但需注意避免毛刺现象。

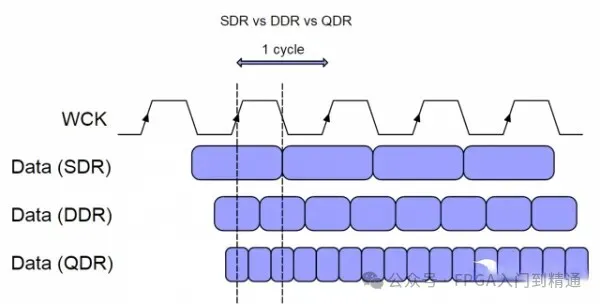

六、双边沿时钟的探索

双边沿时钟允许在时钟的上升沿和下降沿都进行数据传输,如DDR SDRAM。但这种设计复杂度高,对时钟质量要求严格。

七、Verilog时钟设计示例

以下是一个基于Verilog的数字时钟设计示例,展示了时分秒的计数和校准功能:

module digital_clock(

input wire clk, // 外部时钟输入

input wire rst_n, // 复位信号

input wire set, // 设置信号

input [9:0] set_time, // 设置的时间值

output reg [7:0] display_hour, // 显示小时

output reg [7:0] display_min, // 显示分钟

output reg [7:0] display_sec // 显示秒

);

// 内部计数器和时钟分频逻辑...

endmodule

八、时钟设计的优化策略

1、时钟树优化

合理设计时钟树,减少时钟信号的传播延迟和偏移。

2、时钟门控技术

在不需要时钟信号时关闭它们,降低功耗。

3、时钟域交叉

采用适当的同步技术,避免亚稳态。