文章来源: FPGA入门到精通

在FPGA设计和仿真的征途上,调试信息的实时显示是我们不可或缺的导航工具。

本文将深入剖析Verilog中的显示任务函数,结合丰富的实例,让大家迅速掌握这些强大的调试助手。

一、Verilog显示任务概览

Verilog提供了四种主要的系统任务函数来打印调试信息:

$display 、 $write 、 $strobe 和 $monitor

这些任务函数是FPGA开发者在进行仿真和调试时的得力助手。

二、$display 任务:多功能的显示能手

$display 类似于C语言中的 printf 函数,支持丰富的格式化输出。

它可以直接打印字符串,也可以在字符串中指定变量的格式进行打印。

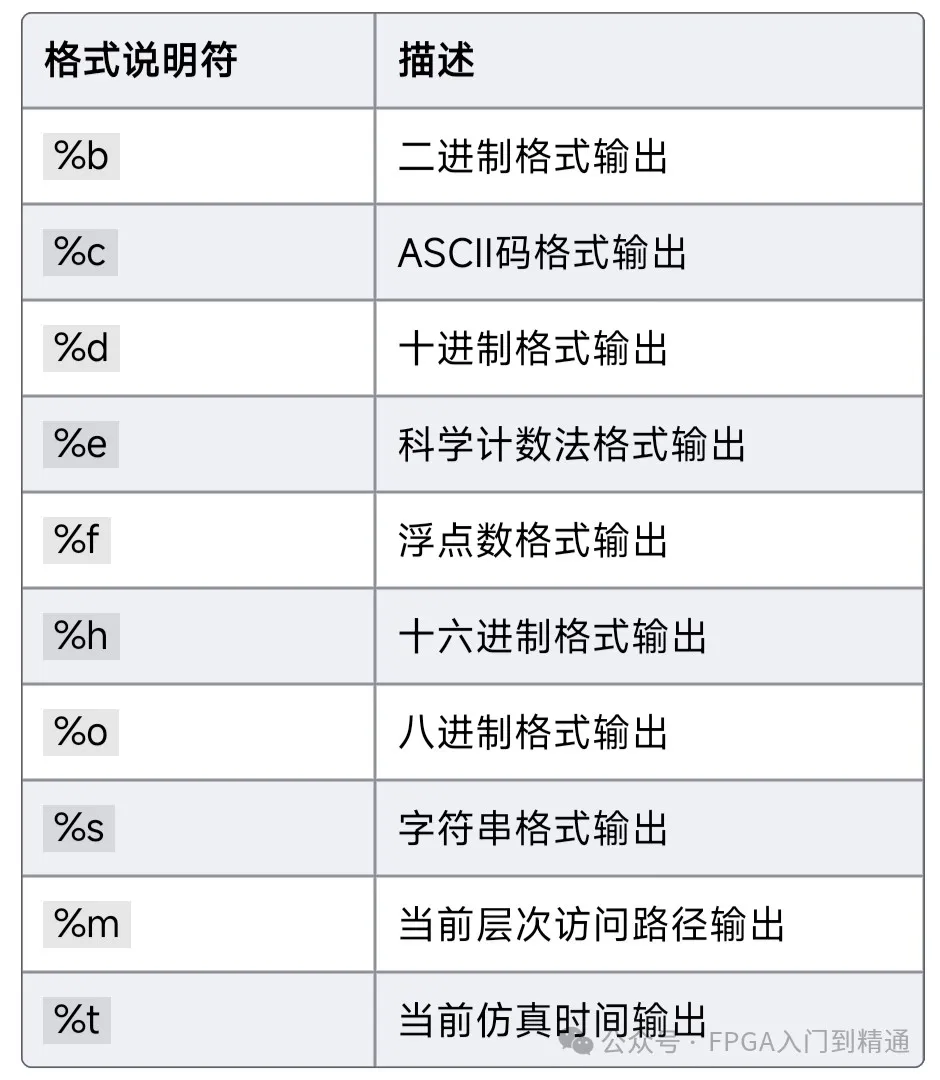

常用的输出格式如下:

转义序列如下:

initial begin

$display("Simulation starts at time %0t", $time);

$display("Binary value of num: %b", num);

end

三、$write 任务:连续输出的巧匠

$write 的使用方式与 $display 完全一致,唯一的区别在于它不会在信息末尾自动换行。

这使得 $write 非常适合在需要连续输出多条信息时使用。

initial begin

$write("Continuous message: ");

$write("Part 1");

$write(" Part 2");

$write(" at time ");

$write(%0t); // 使用转义字符%t输出当前时间

$display; // 最后换行

end

四、$strobe 任务:选通显示的精准捕手

$strobe 是一个在当前仿真时间步结束时打印变量最终值的显示任务。

与 $display 相比, $strobe 的显示时机更晚,可以捕获到非阻塞赋值的最终结果。

always @(posedge clk) begin

if (trigger) begin

$strobe("Triggered at time: %0t, final value of signal: %0d", $time, signal);

end

end

五、$monitor 任务:持续监测的忠诚哨兵

$monitor 是一个持续监测变量变化并打印信息的任务。

每当被监测的变量值发生变化时, $monitor 就会输出当前的仿真时间和变量值。

initial begin

$monitor("Time: %0t, Signal a: %0b, Signal b: %0b", $time, a, b);

end

六、实战技巧分享

在FPGA开发中,合理使用显示任务能够极大提高调试效率。

利用 $monitor 持续监控关键信号,以便快速定位问题。

结合 $display 和 $write 实现多行和单行的输出控制。

使用格式说明符和转义序列清晰展示信号的数值和状态。

在长时间运行的仿真中,可以使用文件I/O记录关键数据,便于后续分析。