文章来源:OpenFPGA

在当今嵌入式开发领域,工具链的演进日新月异。尽管我们之前主要关注Vitis的嵌入式流程,但Vitis Unified平台实际上提供了更广泛的功能,特别适用于Versal、MPSoC、Kria SoM和Alveo等平台的系统开发。

与传统的嵌入式软件开发不同,Vitis Unified允许我们在一个系统方案中同时集成:

嵌入式软件(PS端应用)

可编程逻辑(PL)内核(通过HLS或RTL方式开发)

AI Engine图应用(针对Versal架构)

通过Vitis的异构系统开发,我们可以灵活地整合不同的计算资源,构建完整的系统解决方案。

异构系统开发的输出形式

UltraScale+ MPSoC 和 Kria SoM 平台:输出为 XCLBin 文件(内核二进制包)

Versal 平台:输出为XSA文件

对于自定义的Versal平台,还可以将Vitis设计导出为VMA(Vitis Metadata Archive),并重新导入Vivado进行进一步分析。

无论采用哪种形式,Vitis底层都调用Vivado,开发者可以在不同阶段手动干预,定制硬件实现细节。

核心概念快速了解

要高效使用Vitis异构系统设计流程,需要掌握以下概念:

Extensible Platform(可扩展平台):允许用户添加PL内核或AI应用的目标平台。

Fixed Platform(固定平台):包含完整硬件设计、操作系统、库和启动文件。

Kernel Image:在Kria SoM、UltraScale+ MPSoC上运行的嵌入式Linux内核镜像。

PS Application:运行在ARM Cortex-A核上的软件应用,负责配置和控制PL内核及AI Engine。

RootFS:嵌入式Linux内核挂载的根文件系统。

SysRoot:RootFS的精简版,只包含开发编译需要的库和头文件。

Vitis Compiler (V++):编译PL内核并链接AI Graph的专用编译器。

XRT(Xilinx Run Time):实现OS与硬件设计中PL内核/AI Graph的数据、状态交互的运行时库。

Xilinx Support Archive(XSA):Vivado导出的硬件平台容器文件。

整个异构系统流程基于PetaLinux,因此需要在Linux主机(如Ubuntu 22.04 LTS)或虚拟机中进行开发。

快速体验:向量加法示例

为了快速体验Vitis异构系统开发流程,我们可以构建一个简单的向量加法(Vector Add)应用。

下载公共资源:AMD官网提供了常用的Kernel Image、RootFS、SysRoot及可扩展平台,可以直接下载使用。

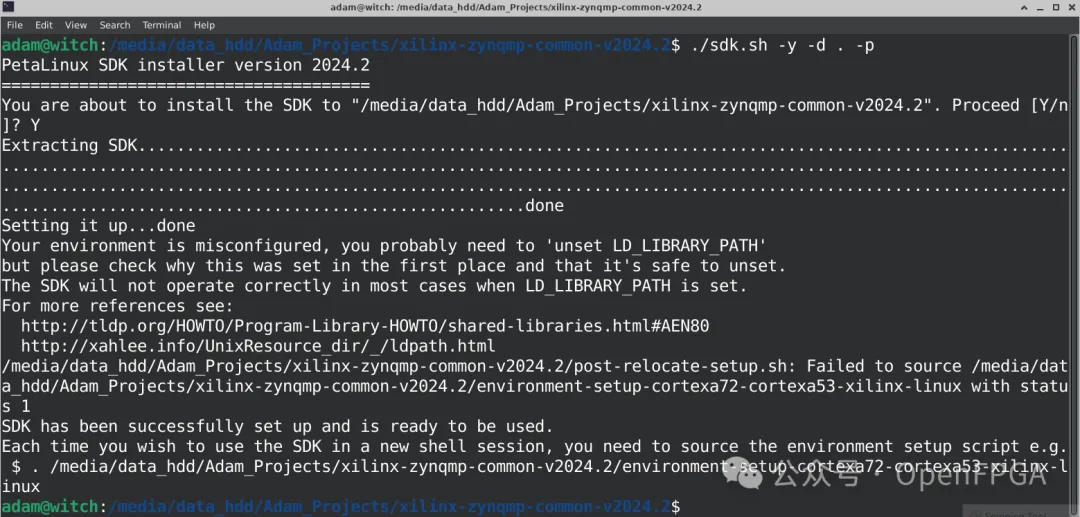

生成SysRoot:运行下载包中的 sdk.sh 脚本,几分钟后完成SysRoot构建。

接下来需要在 Vitis 中根据所包含的示例创建一个新的系统设计项目。

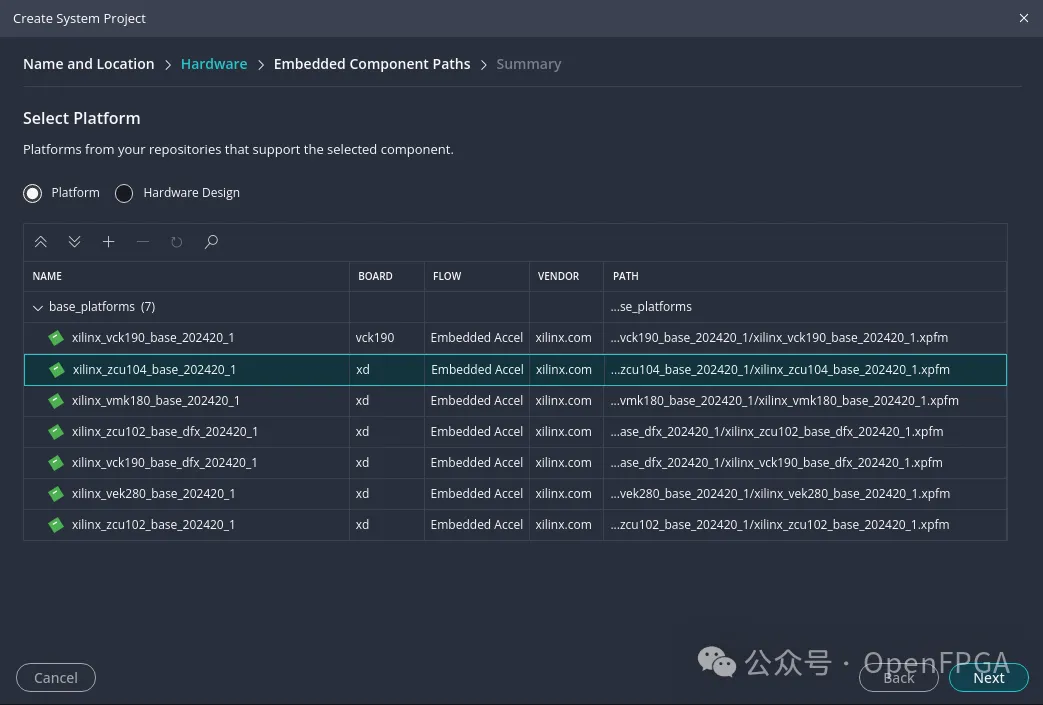

命名项目并选择位置。

在这个例子中,将选择 ZCU104 作为目标板。

提供image、sysroot 和 rootfs 的路径。

单击“完成”

这将打开基于向量加法的 Vitis 示例系统设计示例。

在 Vitis Explorer 中,将看到三个元素。最顶部是整体应用程序,包含整体应用程序的所有设置。其次是主机应用程序,它在处理器核心上运行,是传统的嵌入式软件应用程序。不同之处在于它也提供数据,并配置和控制 PL 中的内核。这由最后一个元素定义,即 HLS 中定义的 PL 内核。

这个例子包含了构建应用程序所需的一切,在2024.2中有两个主要路径可以构建应用程序。

第一个步骤是硬件仿真,这个过程使用 Qemu 和 Vivado 仿真器来共同仿真创建的设计。第二个步骤是构建可部署的镜像,在本博客中,同时进行这两个步骤。

首先,构建了针对硬件仿真的系统设计,可以启动仿真器,运行应用程序,正如所说,我想记录波形,打开 Vivado 仿真器以便探索波形。

一旦对硬件仿真的构建感到满意并且测试通过,就会构建可部署的硬件。

这提供了完整的 SD 卡映像,可以在 ZCU104 开发板上启动。当然,在编译过程结束时,它会提供一些报告,详细说明实现细节。

这样就结束了~

总结

随着Vitis异构系统设计流程的不断成熟,我们可以更加灵活地结合PS、PL、AI资源,开发出复杂而高效的异构加速系统。未来,进一步探索自定义平台、开发自定义内核,将极大扩展我们的系统能力边界。

下一步计划:将深入学习自定义平台开发和PL核集成,真正发挥异构计算的全部潜力!