如何做好Verilog的代码检视(code review)

judy 在 周四, 09/08/2022 - 11:10 提交

无论是FPGA还是ASIC的开发者,都或多或少地做过代码检视(code review)。

无论是FPGA还是ASIC的开发者,都或多或少地做过代码检视(code review)。

在异步跨时钟域场合,对于控制信号(通常位宽为1bit)常使用双触发器的方式完成跨时钟域操作

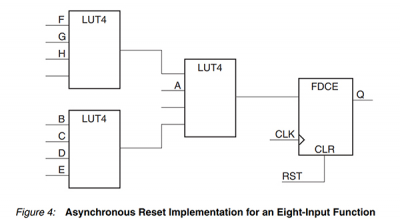

实现FPGA 设计最大性能化的一个重要因素是正确的RTL 编码设计。

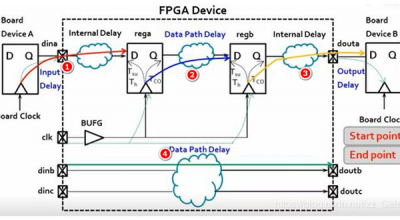

今天我们就来详细分析一下,这个约束应该如何使用。

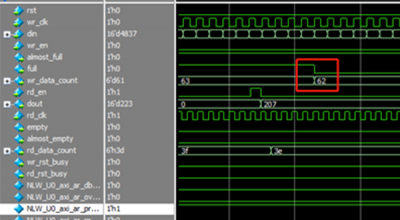

以前从来没有这么细扣过,认识比较肤浅,通过几天对Xilinx IP核的仿制,对异步FIFO有了更深刻的认识。

无论是搞FPGA还是ASIC的工程师,都知道代码完成了要搞单元仿真(UT),但是怎么搞?

Xilinx LogiCORE IP快速傅立叶变换核实现了Cooley-Tukey-FFT算法,这是计算离散傅立叶变换(DFT)的有效方法

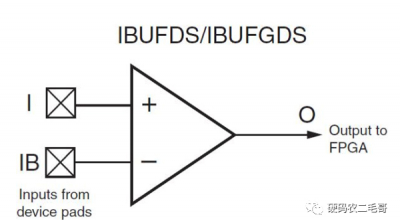

FPGA开发中经常会用到LVDS信号,本文分别介绍intel fpga和xilinx fpga的LVDS信号处理方法。

数字电路根据逻辑功能的不同特点,可以分成两大类:组合逻辑电路与时序逻辑电路

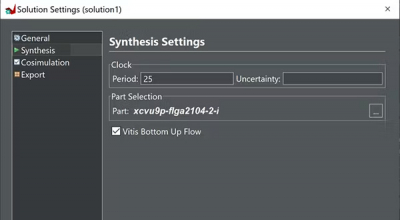

Vitis HLS是Vitis AI重要组成部分,所以我们将重点介绍Vitis HLS。