注意:本文所有内容皆来源于Xilinx工程师,如需转载,请写明出处作者及赛灵思论坛链接并发邮件èï¼æªç»Xilinxåèä½æ人许å¯ï¼ç¦æ¢ç¨ä½åä¸ç¨éã

Zynq UltraScale+ MPSoC â IPIå¨å¼æå¤æ ¸ä¸çåºç¨

æ¬ç¯å°è®¨è®ºMPSoCä¸IPIçåºç¨ãé¦å æ¾æ¸ è¿éçIPIä¸æ¯å°ä¼ä¼´ä»¬çç¥çVivado IPI Design FlowçIPIï¼IP Integratorï¼ï¼èæ¯Inter-Processor Interruptï¼æ¯MPSoCä¸ç¨æ¥å¨å¼æå¤æ ¸ç³»ç»ä¸ä»¥ä¸æçå½¢å¼å®ç°å°æ¹éä¿¡æ¯äº¤äºçç»æåå ã

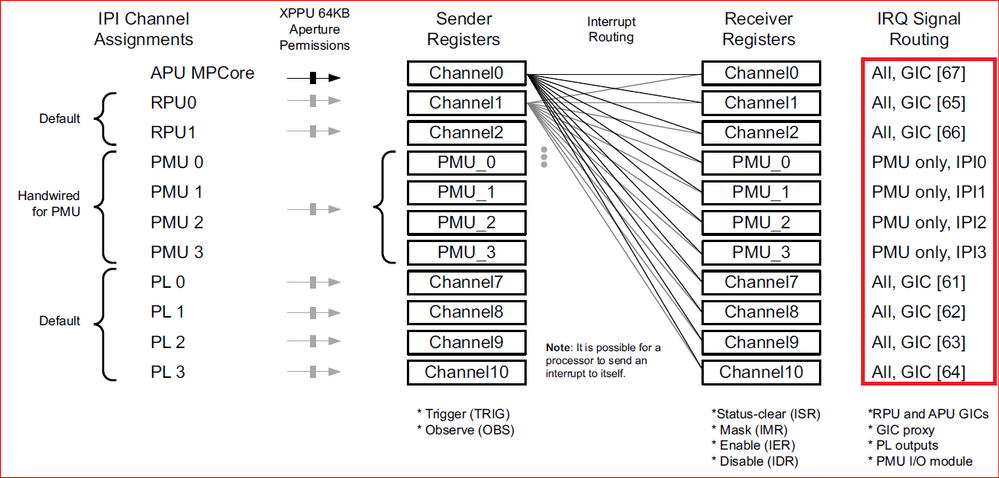

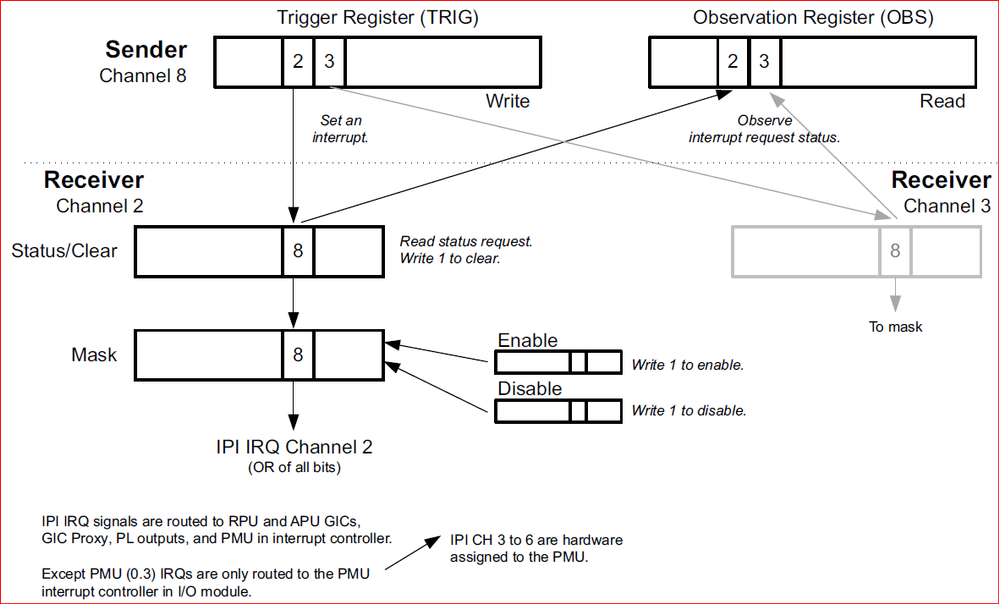

IPIå ±æä¾11个channelï¼å ¶ä¸4个channelï¼3~6ï¼åºå®åé ç»PMUï¼å ¶ä»7个channelï¼0~2ï¼7~10ï¼å¯åé ç»APU/RPU/PLæ¥æ§å¶ãæ¯ä¸ªChannelä¸å å«æ6个å¯ä¾ç¨æ·è®¿é®çå¯åå¨ï¼åæSenderï¼TRIG/OBSï¼åReceiverï¼ISR/IMR/IER/IDRï¼ä¸¤ç»ãæ¯ä¸ªChannelçæ¯ä¸ªå¯åå¨ä¸ï¼é½æä¸å ¶ä»channelç对åºæ§å¶/ç¶æä½ï¼å¦ä¸å¾æ示ã

å¯åå¨æä½ä¸ä¸æååºè¿ç¨å¯åèä¸å¾ãæ¯å¦ç±Channel 8åChannel 2åèµ·ä¸æ请æ±ï¼Channel 8çMasteråå ¶TRIGå¯åå¨çBIT9ï¼å¯¹åºChannel 2ï¼åå ¥1ï¼å³åChannel 2çMasteråèµ·ä¸æ请æ±ãChannel 2çMasteræ¶å°ä¸æåï¼å¯æ¥è¯¢ISRçç¶æä½ä»¥ç¡®å®ä¸ææ¥æºã

IPIç³»ç»ä¸ï¼é¤Channel 3~6å¤ï¼æ¯ä¸ªChannel对åºä¸ç»Message Buffer Agentï¼æ¯ç»æ8个Requesterå8个Responderï¼æ¯ä¸ªBuffer为32Bytesãå¨ä¸æè¿ç¨ä¸ï¼å¯åå©è¿äºBufferï¼å®ç°ä¸¤ä¸ªProcessoré´çä¿¡æ¯äº¤äºã

æ´å¤è¯¦ç»å 容å¯åèUG1085->Chapter 13: Interrupts->IPI Interrupts and Message Buffersç« èã

æ¬ç¯å®ç°IPIåºç¨å°å®æä¸è¿°åè½ï¼

APUæ§å¶IPI-Channel0ï¼RPU0æ§å¶IPI-Channel1ï¼é»è®¤è®¾ç½®ï¼ã

APUåå

¶Requester/Message Bufferå¡«å

ä¿¡æ¯åï¼è§¦åChannel1ä¸æã

RPUæ¶å°ä¸æåï¼è¯»åBufferå

容ï¼å¹¶å¡«å

Responder Bufferï¼è§¦åChannel0ä¸æã

APUæ¶å°ä¸æåï¼è¯»åResponder Bufferå

容ã

ä¸å ±å为ä¸ä¸ªæ¥éª¤ï¼

æ°å»ºVivadoå·¥ç¨ï¼ç¡®å®IPI channelçMasteråé

ã

æ°å»ºåºäºAPUçXSDK Applicationå·¥ç¨ã

æ°å»ºåºäºRPUçXSDK Applicationå·¥ç¨ã

ï¼éäºç¯å¹

ï¼è¿éåªååºæ¯ä¸ªæ¥éª¤ä¸çå

³é®é¨åãï¼

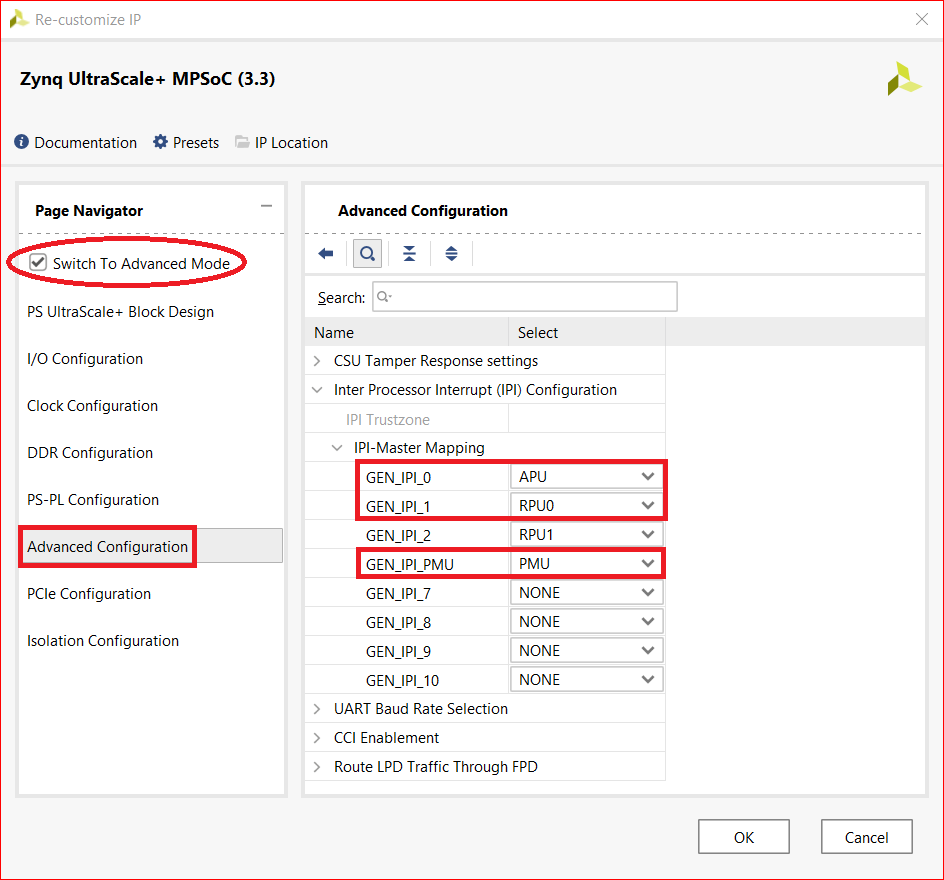

Step1. æ°å»ºVivadoå·¥ç¨ï¼å¨Block Designä¸æ·»å MPSoCï¼å¹¶ç¡®å®MPSoCçé ç½®ä¸IPIçMaster设置ãå¦ä¸å¾æ示ã

IPIç设置é»è®¤æ¯ä¸æ¾ç¤ºçï¼éè¦åæ¢è³Advanced Modeï¼å¨Advanced Configurationé项ä¸ï¼å°±å¯ä»¥æ¾å°Inter Processor Interrupt(IPI) Configurationãé»è®¤æ åµä¸ï¼Channel 0/1/2åå«åé ç»APU/RPU0/RPU1ãè¿éæ们就éç¨é»è®¤é ç½®ãå°ä¼ä¼´ä»¬ä¹å¯ä»¥æ ¹æ®èªå·±çéæ±æ¥é ç½®Masterã

确认å®æåï¼ç»§ç»å®æå®æ´çMPSoCçBlock Design设计ã使ç¨å°PLçç´å°äº§çå®BITSTREAMï¼æªä½¿ç¨PLçï¼Generate Output Productå³å¯ï¼å½ç¶ä¹è¦Create HDL Wrapperã

æ¥ä¸æ¥ï¼Export Hardwareï¼ç¶åLaunch SDKãåç»çStep2åStep3顺åºæ å åã

Step2. æ°å»ºåºäºAPUçXSDK Applicationå·¥ç¨ï¼å¹¶å¯¼å ¥apu_ipi.cã

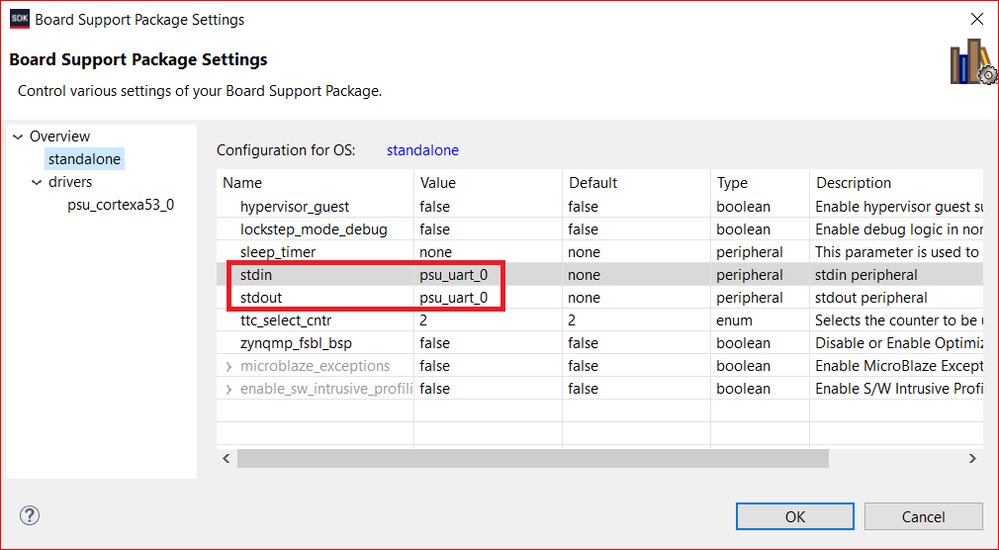

注ææ°å»ºå·¥ç¨æ¶æå®Processor为psu_cortexa53_0ï¼å¹¶ç¡®ä¿BSP设置ä¸stdin/stdout为psu_uart_0ï¼ä¸Step3ä¸ä¸ä¸æ ·å°±è¡ï¼ãï¼æ¥å®æè¿ä¸ªå®éªçæ¶åç¨çZCU106æ¿å¡ï¼æä¾äºä¸¤ä¸ªPSçUARTå¯ä»¥ç¨ãå°ä¼ä¼´ä»¬èªå·±çå¼åæ¿å¦æ没æ2个UARTï¼Step2/3å ¶ä¸ä¸ä¸ªå¯è®¾ç½®ä¸ºpsu_coresight_0ï¼åå©Coresightå¨Consoleä¸ç´æ¥æ¥çæå°ä¿¡æ¯ãï¼

ä¸èµ·æ¥çä¸ä¸APUçå·¥ä½è¿ç¨ï¼

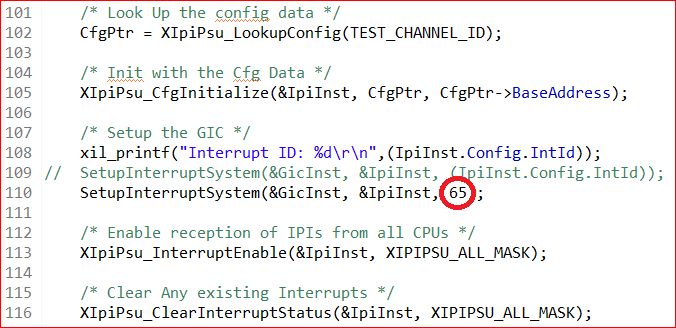

ï¼1ï¼åå§åIPI设å¤ï¼åå§åä¸æç³»ç»ï¼ä½¿è½IPIç¸å ³ä¸æãæ¤å¤ä¸æå·ä¸º67ï¼ä¸GUIä¸é ç½®çAPU对åºçChannel 0ä¸è´ãä¸æå·å¯åèFigure 1ã

Figure 7

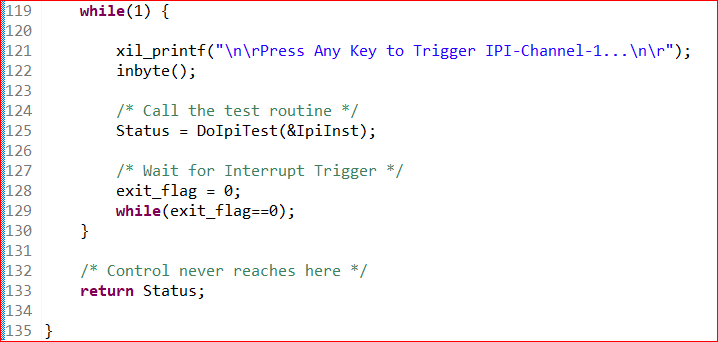

ï¼2ï¼çå¾ æ¥åé®çè¾å ¥ï¼ä»¥è§¦åIPIå·¥ä½ã

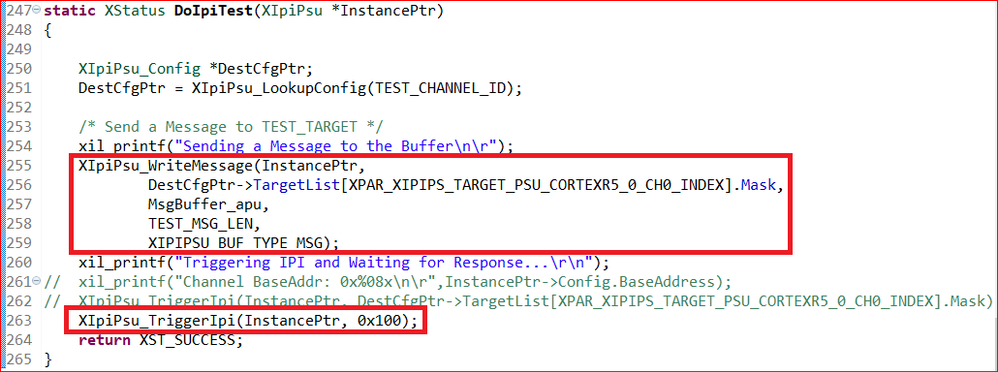

ï¼3ï¼æ¥åé®çè¾å ¥åï¼è°ç¨DoIpiTest()ï¼å®æå°Messageåå ¥Bufferï¼è§¦å对RPU0çIPIä¸æã

ï¼4ï¼çå¾ RPUè¿åä¸æï¼è¯»ååå¤çMessageã

ï¼5ï¼å®æä¸æ¬¡äº¤äºè¿ç¨ï¼è¿å ¥ä¸ä¸æ¬¡è§¦åçå¾ ã

Step3. æ°å»ºåºäºRPUçXSDK Applicationå·¥ç¨ï¼å¹¶å¯¼å ¥rpu_ipi.cã

注ææ°å»ºå·¥ç¨æ¶æå®Processor为psu_cortexr5_0ã并确ä¿BSP设置ä¸stdin/stdout为psu_uart_1ï¼ä¸Step2ä¸ä¸ä¸æ ·å°±è¡ï¼ã

åæ ·ï¼ä¸èµ·çä¸ä¸RPU主è¦å·¥ä½è¿ç¨ï¼

ï¼1ï¼åå§åIPI设å¤ï¼åå§åç³»ç»ä¸æï¼ä½¿è½IPIç¸å ³ä¸æãæ¤å¤ä¸æå·ä¸º65ï¼ä¸GUIä¸é ç½®çRPU0对åºçChannel 1ä¸è´ãä¸æå·å¯åèFigure 1ã

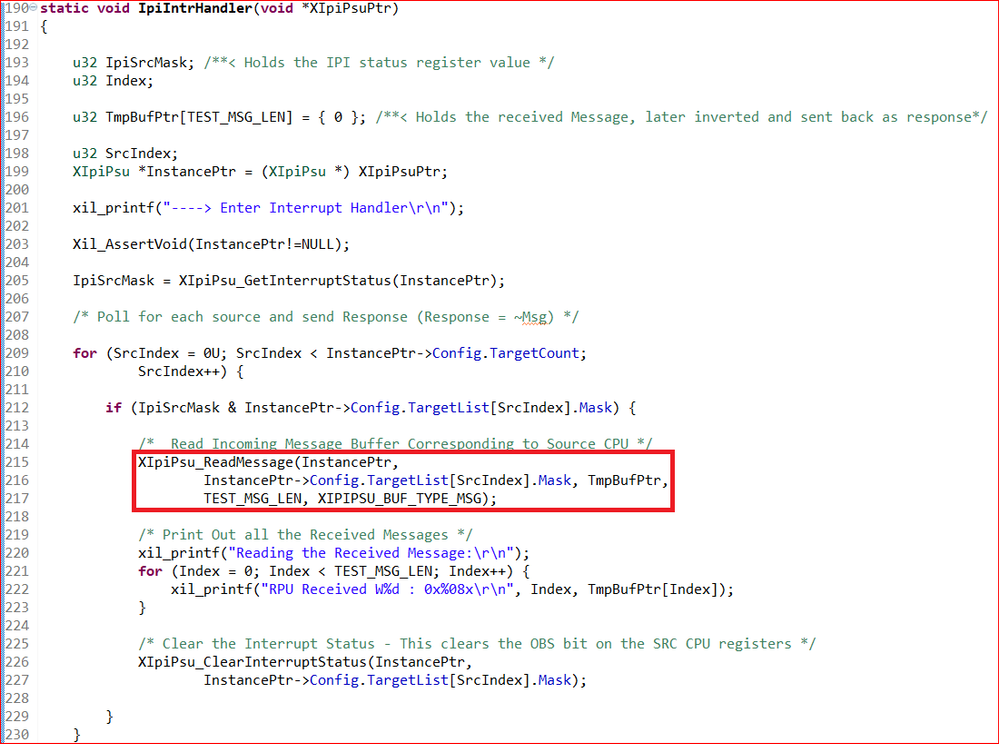

ï¼2ï¼çå¾ æ¥èªAPUçä¸æ请æ±ãæ¶å°ä¸æå读åBufferå 容ï¼å¹¶è°ç¨DoIpiTest()æ§è¡æ°æ®è¿åå¤çã

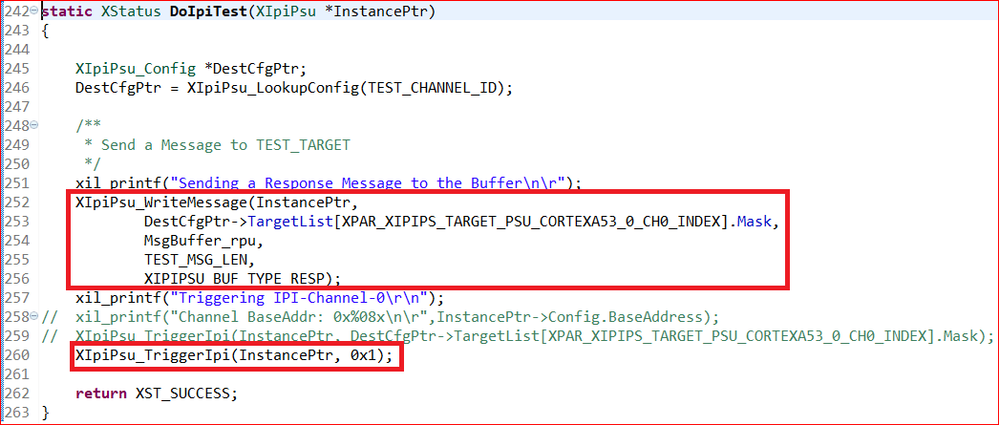

ï¼3ï¼å¨DoIpiTest()ä¸ï¼å°è¿åæ°æ®å¡«å Bufferï¼å¹¶è§¦å对APUçIPIä¸æã

ï¼4ï¼å®æä¸æ¬¡ååºè¿ç¨ï¼è¿å ¥ä¸ä¸æ¬¡ä¸æçå¾ ã

åç¶åï¼å°±æ¯éªè¯ç»æäºãå¯ä»¥Create Boot Imageä»SDå¡ç´æ¥å¯å¨ï¼ä¹å¯ä»¥ç´æ¥éè¿XSDKæ¥Run/Debugï¼è¿éå°±ä¸è¯¦ç»åè¿°è¿ç¨äºï¼ç¸ä¿¡æ¥çè¿ç¯å¸åçå°ä¼ä¼´è¯å®æ足å¤çMPSoCå¼åç»éªï¼ï¼ç´æ¥ä¸è¿è¡ç»æï¼æ¹ä¾¿å¤§å®¶å¯¹ç §ã

PSï¼æ´çè¿ç¨è¿äºä»ä¿ï¼å¦æçæ¼æé®é¢ï¼æ¬¢è¿å°èµçµæä¸æ论å讨论å¦ä¹ ï¼

åå¸å°åï¼https://forums.xilinx.com/t5/Xilinx-%E4%BA%A7%E5%93%81%E8%AE%BE%E8%AE%A1...

æ¤æç« å«æå ·ä½demoï¼è§é件

æç« æ¥æºï¼Â èµçµæä¸æ社åºè®ºå