PL通过NoC读写DDR4实验

实验VIvado工程为“pl_rw_ddr”

1.1硬件介绍

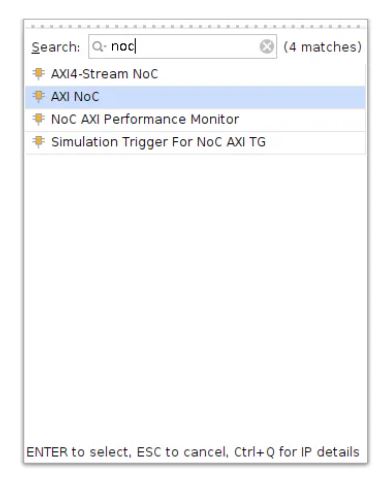

开发板的PL端有4颗16bit ddr4

1.2Vivado工程建立

Versal的DDR4是通过NoC访问,因此需要添加NoC IP进行配置。

1.2.1创建一个Block design并配置NoC

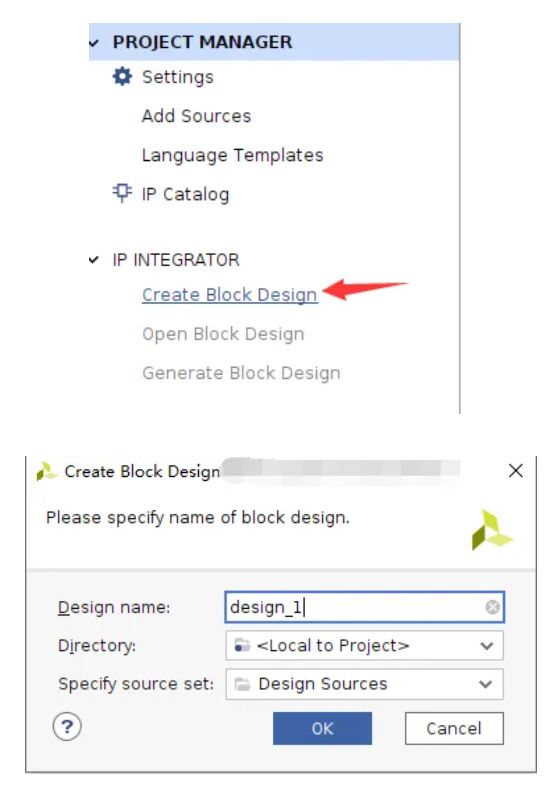

1)选择Create Block Design

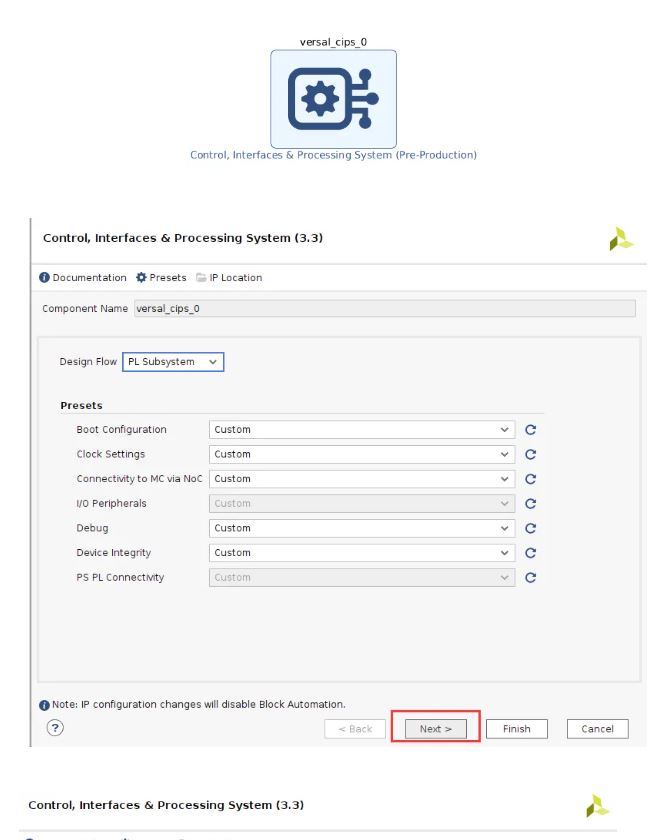

2)添加CIPS

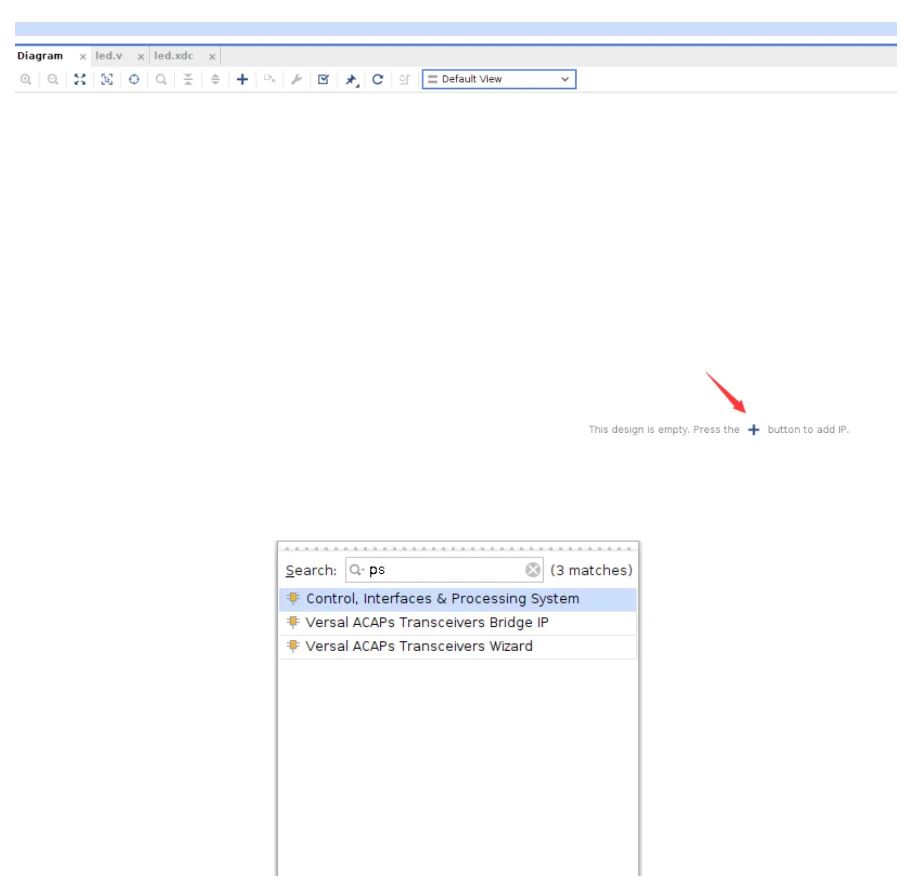

3)双击CIPS,选择PL_Subsystem,只有PL端的逻辑

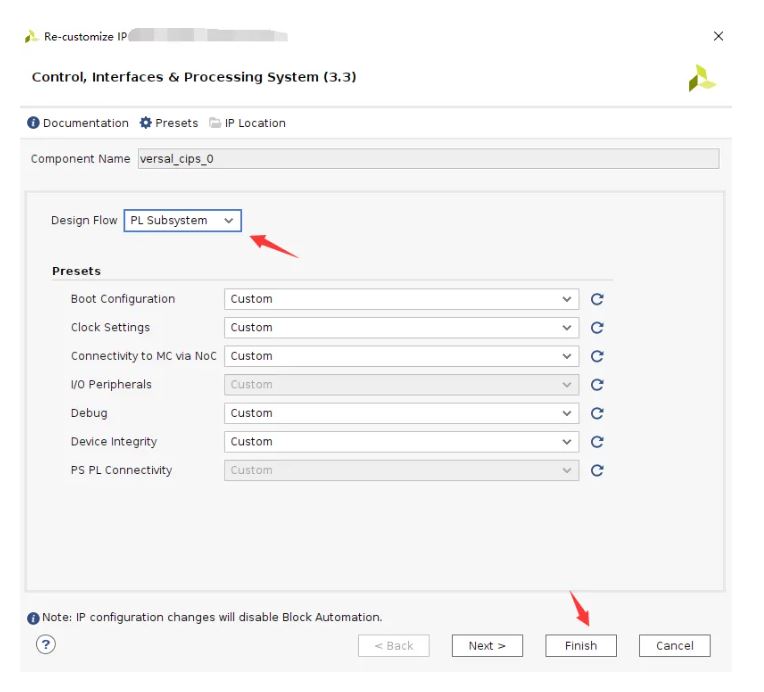

4)添加NoC IP

5)配置NoC

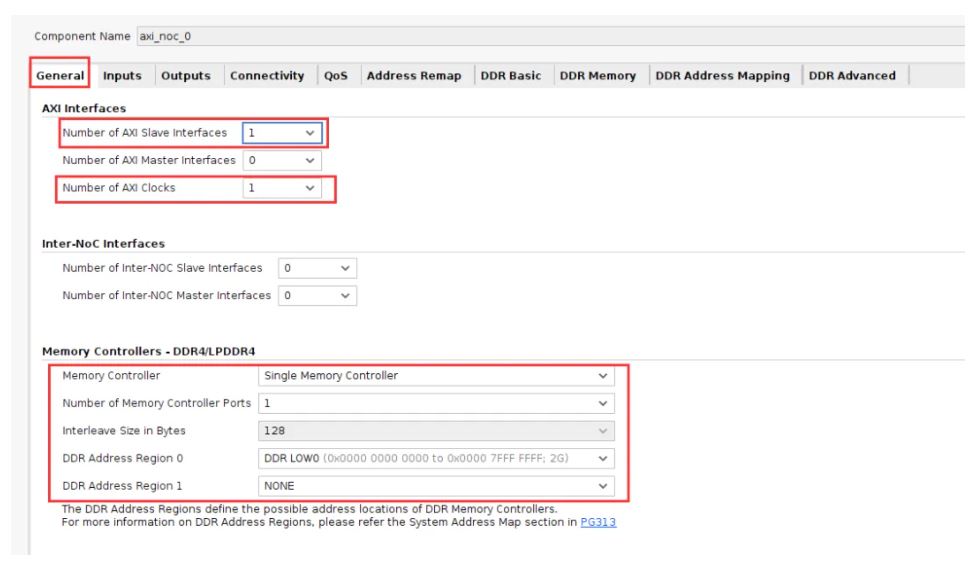

选择一个AXI Slave和AXI Clock,选择”Single Memory Controller”

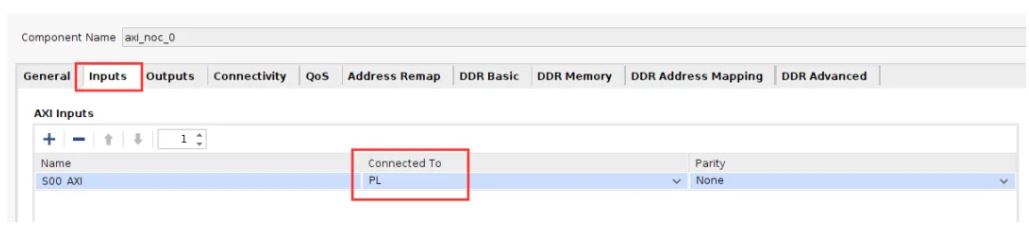

选择Inputs为PL

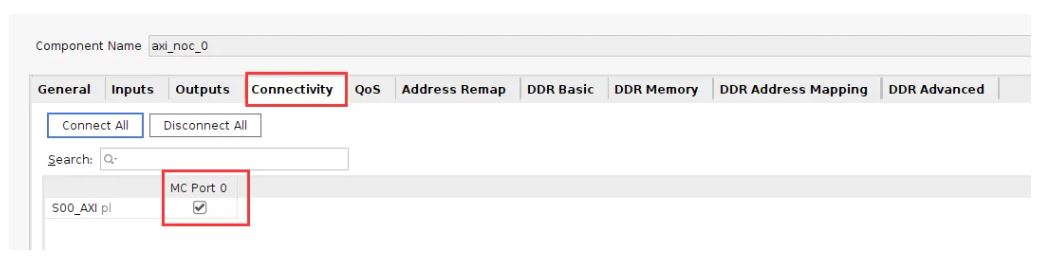

连接port

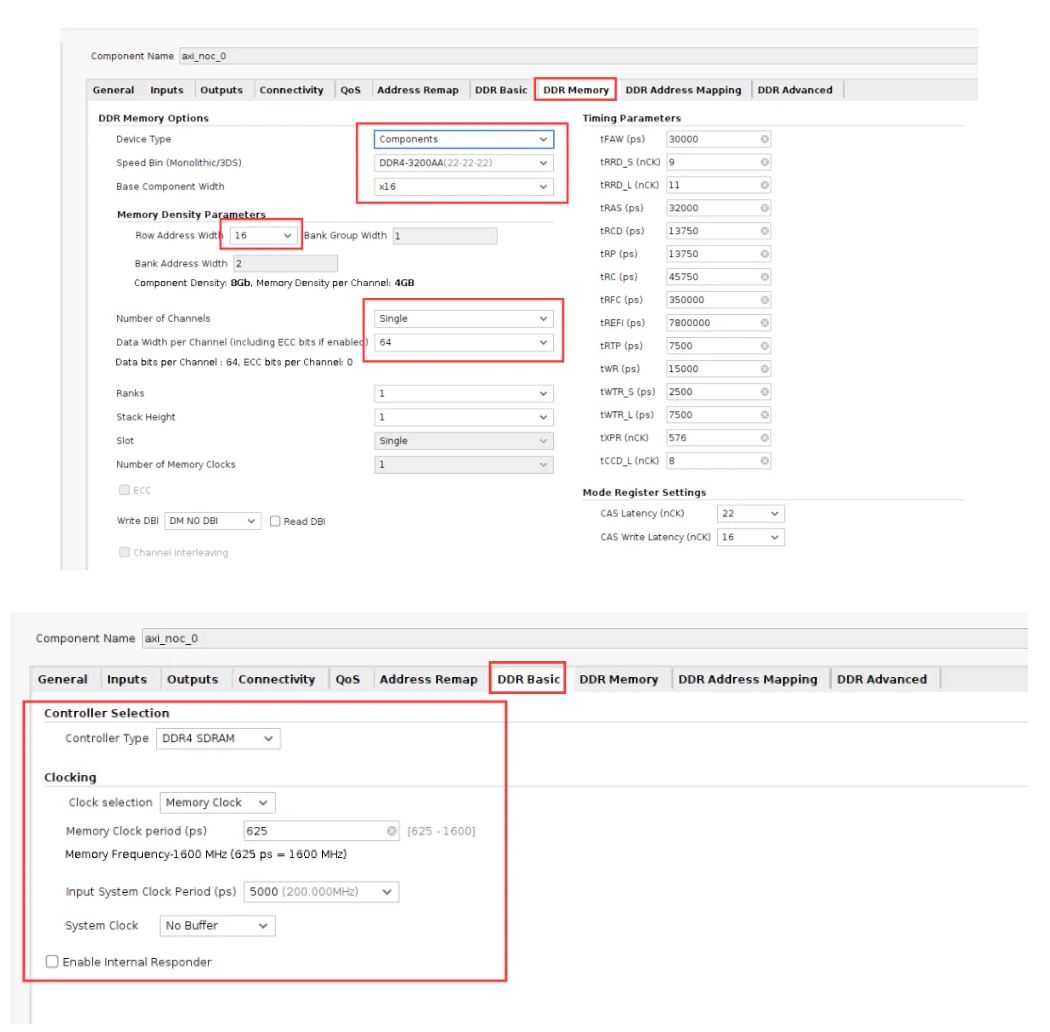

DDR4配置

配置完成,点击OK

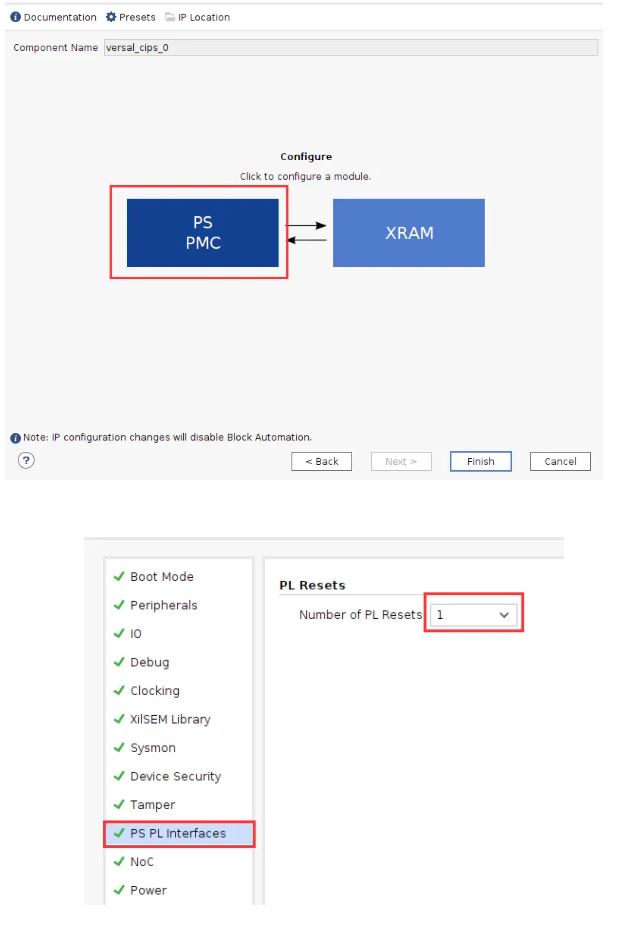

6)配置CIPS,添加复位

点击Finish

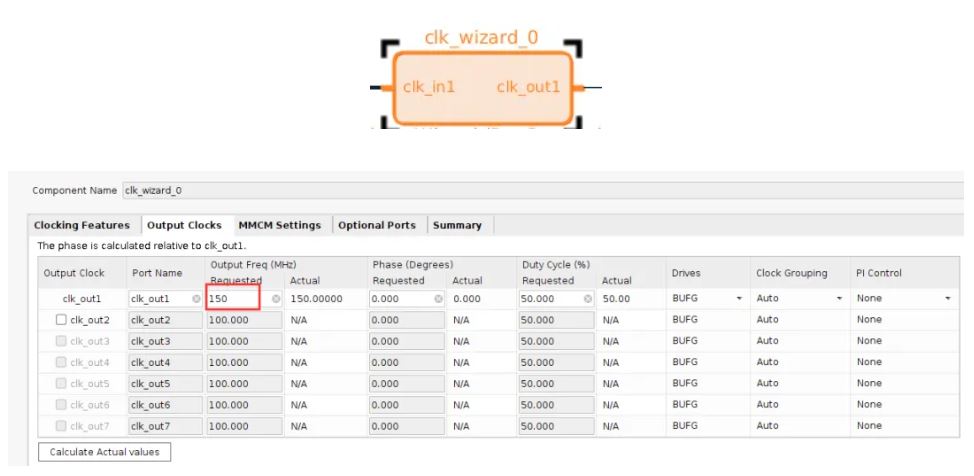

7)添加Clocking Wizard,配置输出时钟150MHz,作为PL端读写时钟

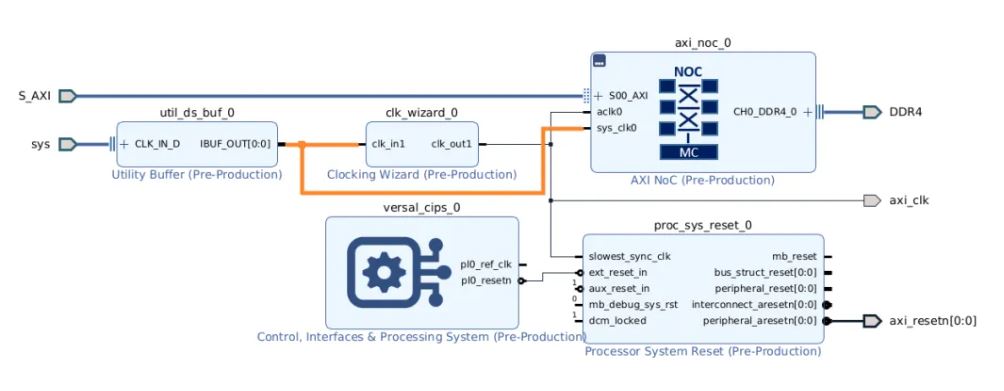

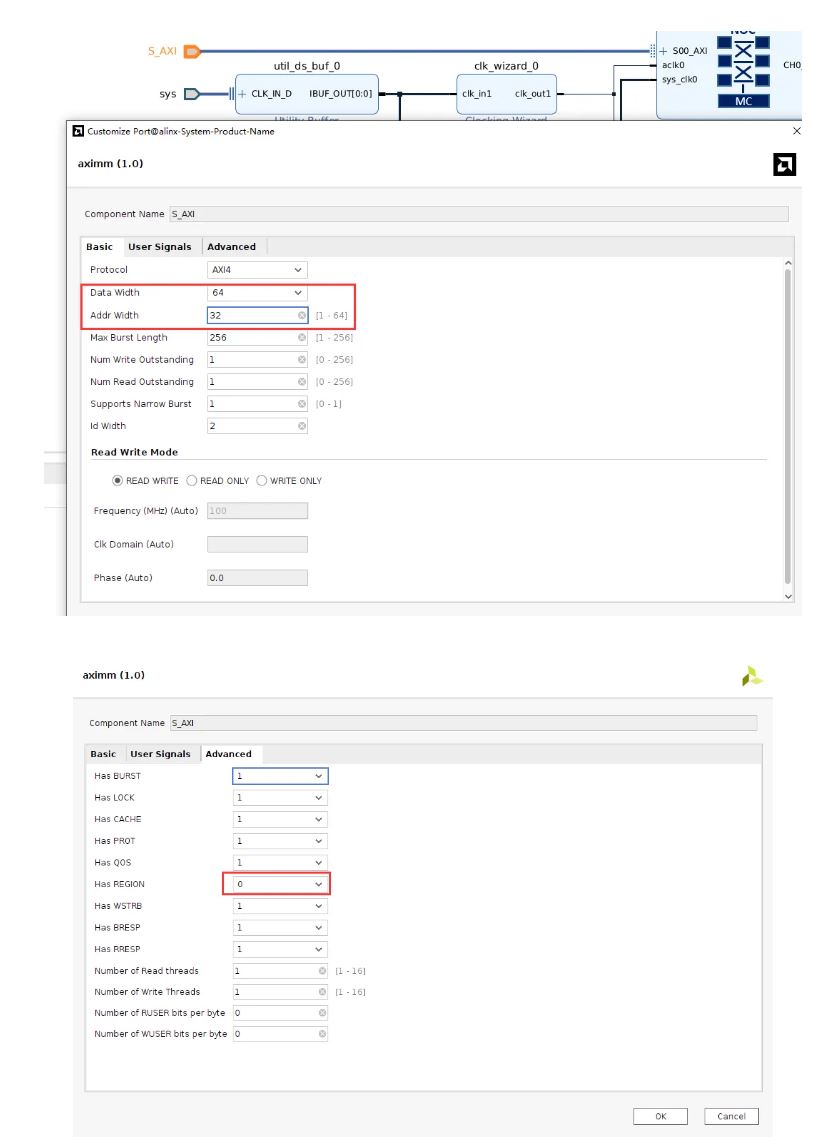

8)添加IBUFDS为NoC和Clocking Wizard提供参考时钟,并导出S00_AXI,CH0_DDR4_0等总线,添加axi_clk,axi_resetn为PL端提供时钟和复位。

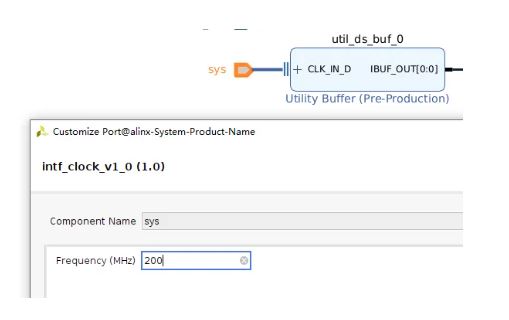

双击参考时钟引脚,并配置频率为200MHz

双击AXI总线,并配置

9)分配地址

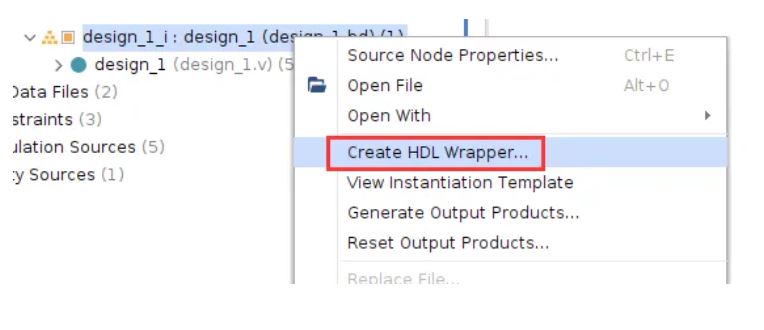

10)Create HDL

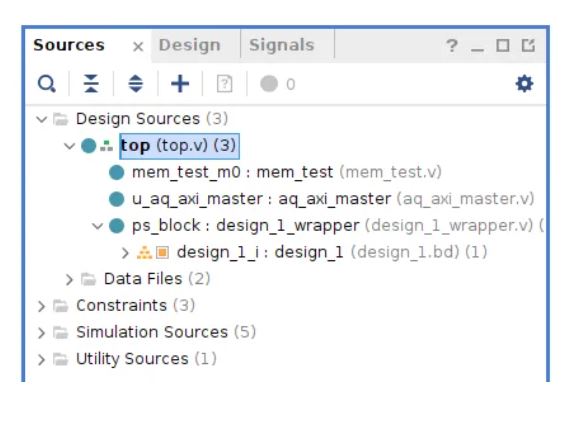

1.2.2添加其他测试代码

其他代码主要功能是读写ddr4并比较数据是否一致,这里不做详细介绍,可参考工程代码。

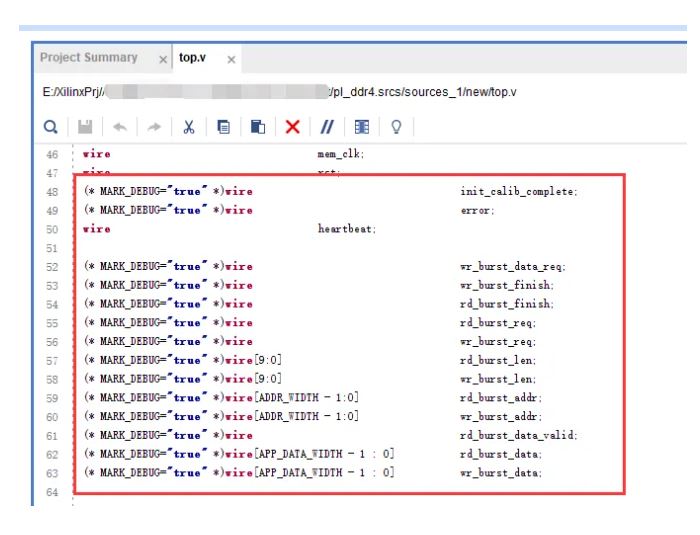

1)在mem_test.v中添加mark_debug调试

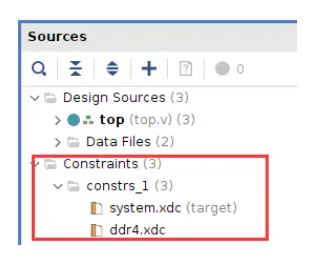

2)引脚绑定

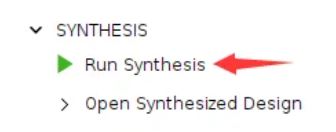

3)综合

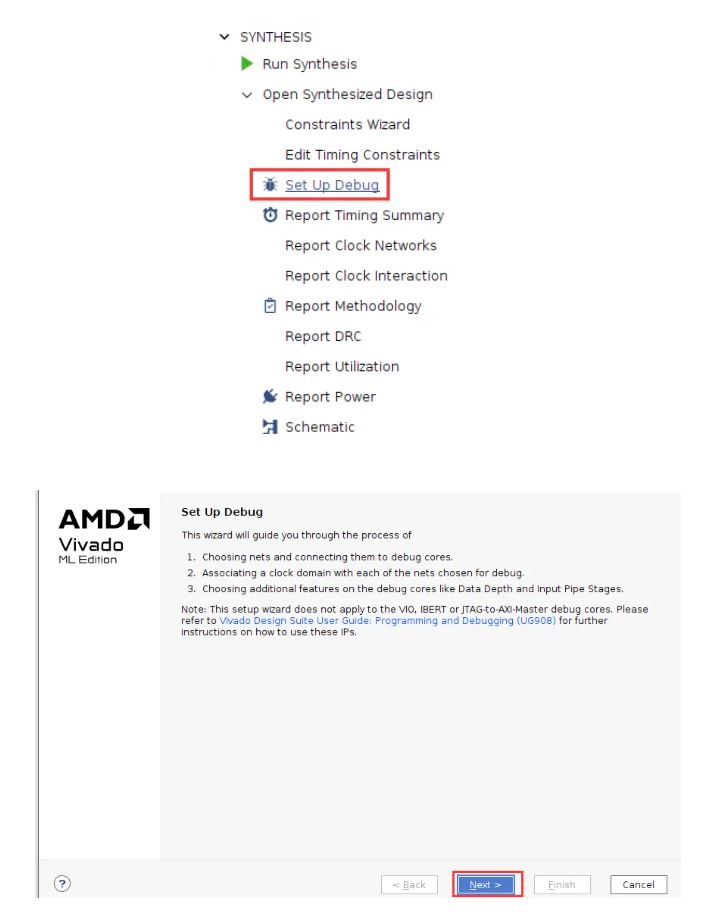

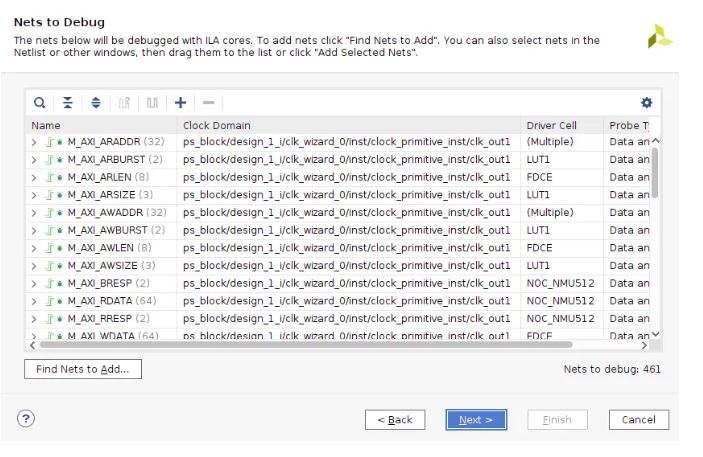

4)综合完成后点击Set up debug

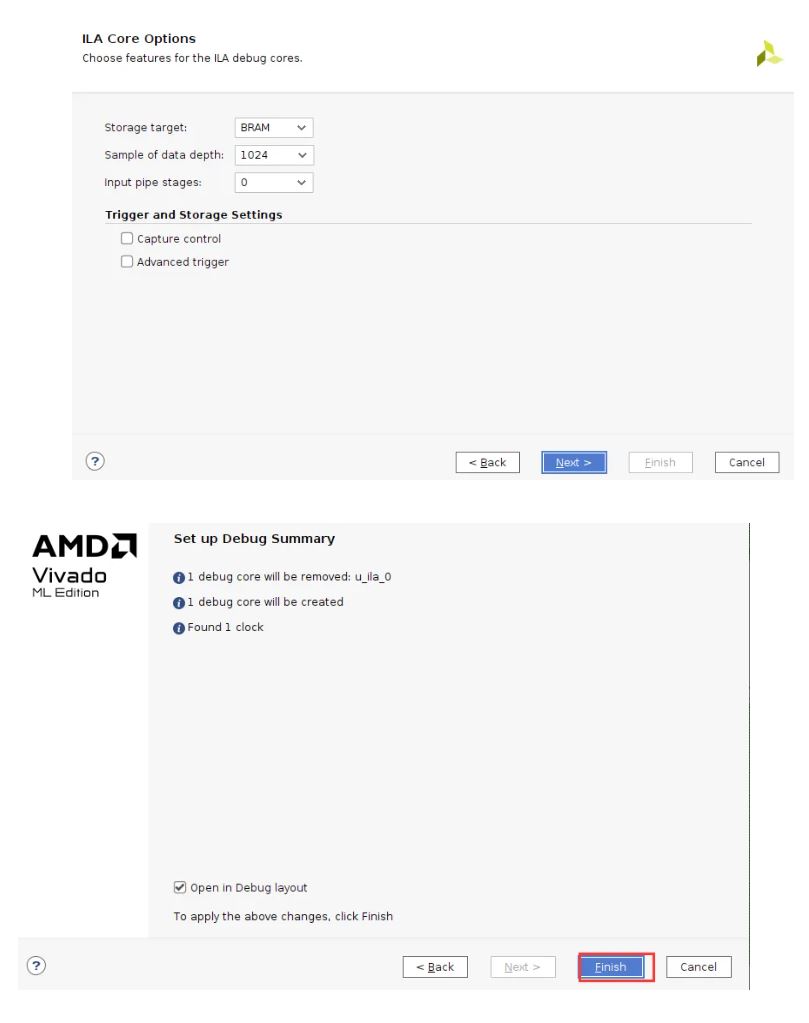

根据需求设置采样点数

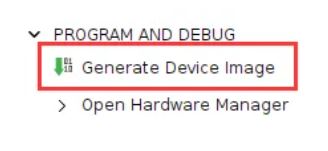

之后保存,并生成pdi文件

1.3下载调试

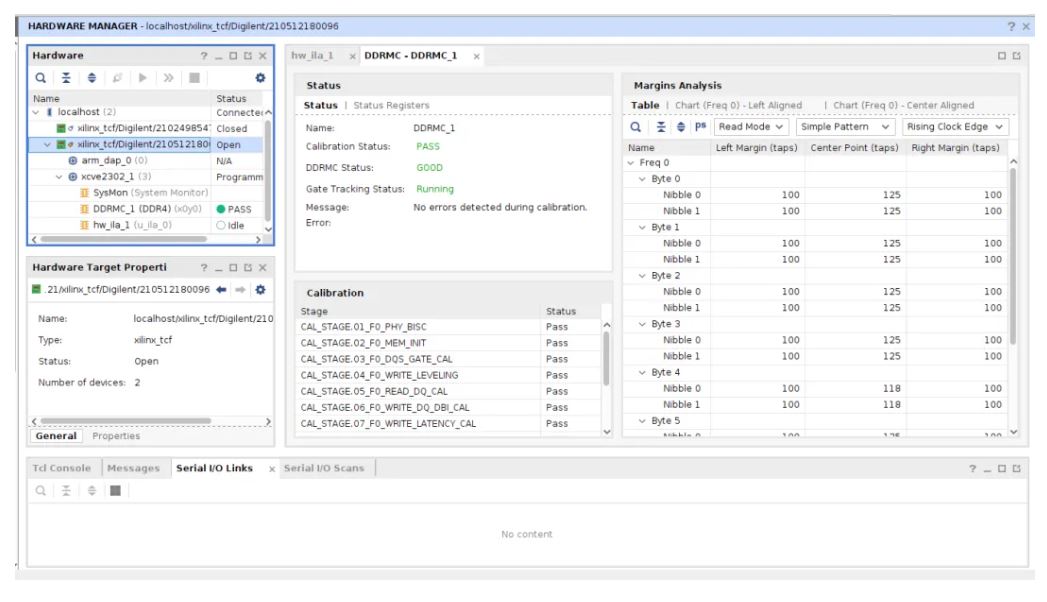

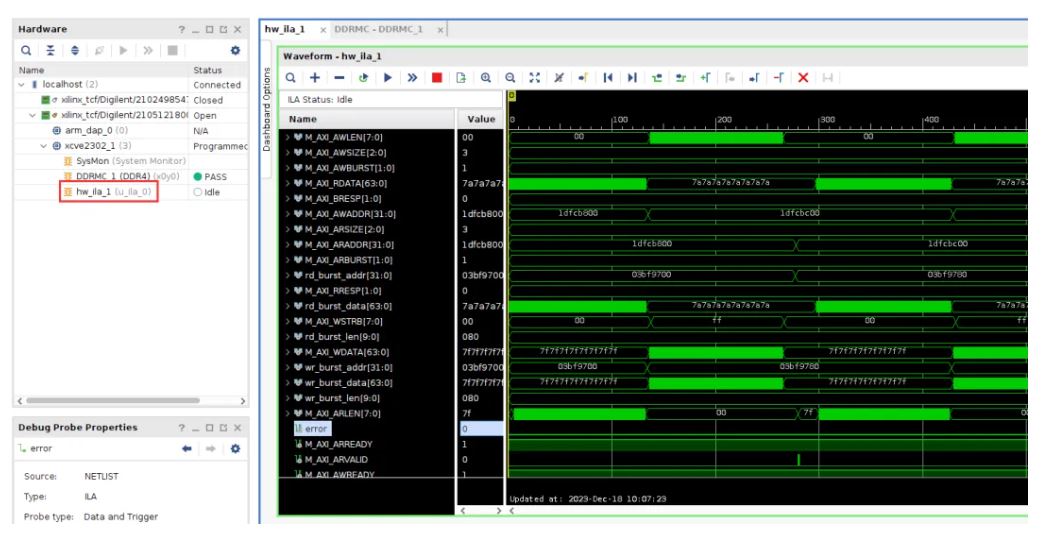

生成pdi文件以后,使用JTAG下载到开发板,在MIG_1窗口会显示DDR4校准等信息

在hw_ila_1中可以查看调试信号

1.4实验总结

本实验通过PL端Verilog代码直接读写ddr4,主要了解NoC的配置方法,如何通过NoC访问DDR4,后续的实验中都要用到此配置。

文章来源:ALINX