作者:Kathy Ren,AMD工程师;来源:AMD开发者社区

在Vesal器件的DDRMC DDR4/LPDDR4接口上,控制器的系统时钟源通常是由片外的差分时钟所提供的;除此之外,还可以由CIPS生成一个内部HSM1参考时钟。在这种情况下,可以节省PCB板上空间以及时钟产生芯片。这个方案从Vivado 2023.1开始支持。

HSM1时钟可以给所有的DDRMC提供系统时钟,但是,对于共用HSM1时钟的DDRMC来说,系统时钟的频率必须是相同的。这个时钟频率的范围是100-200MHz,所以,相应的HSM1时钟频率也要设置在100-200MHz。

使能和设置HSM1时钟的步骤如下:

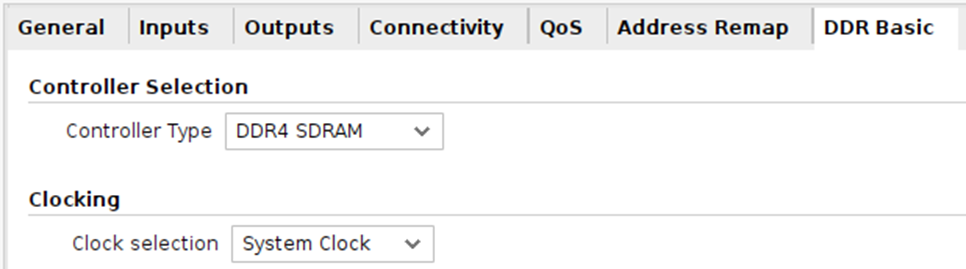

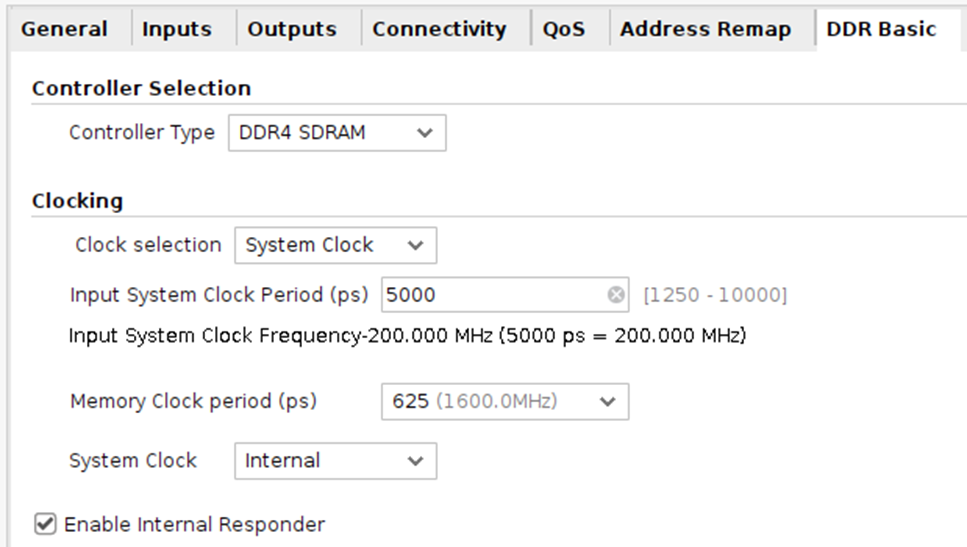

1. 在Block design中打开AXI NOC IP, 选择“DDR Basic”选项卡

2. 修改“Clock selection”选项为“System Clock”

3. 按照DDR4接口速率设置“Memory Clock Period”,然后再设置“Input System Clock Period”(大多数data rate情况下可以选7500ps或者5000ps)。如下图这个例子中,Input System Clock Period设为 5000ps。

4. 选择OK按钮退出NOC IP wizard

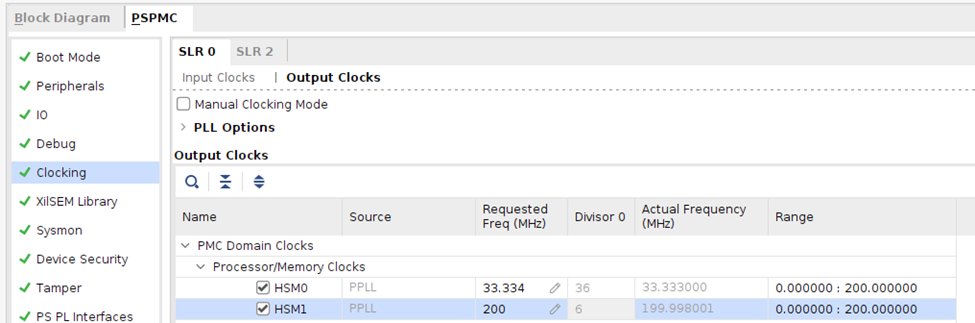

5. 在Block design中,双击打开CIPS IP,选择“PS PMC configuration”按钮,然后选择PSPMC选项卡Clocking部分的 SLR0。

6. 勾选使能HSM1时钟,设置Requested Freq”为200MHz,和NOC IP中“Input System Clock Period”设置保持一致。

7. 然后选择NoC ->SLR0,勾选“DDRMC HSM1 Clock Port ”

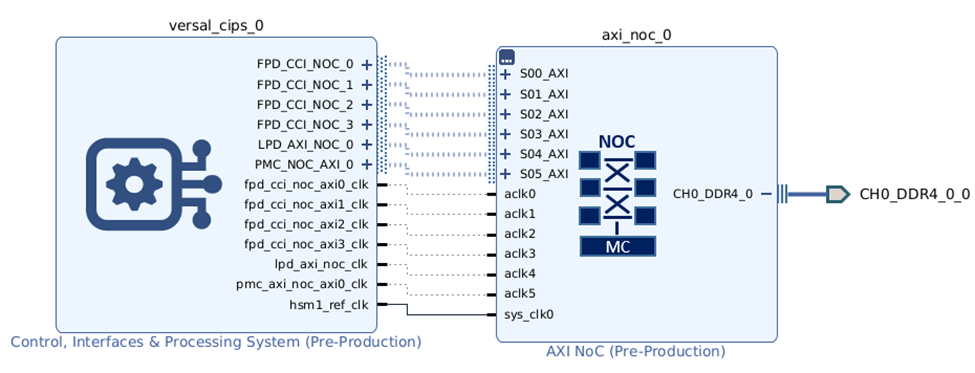

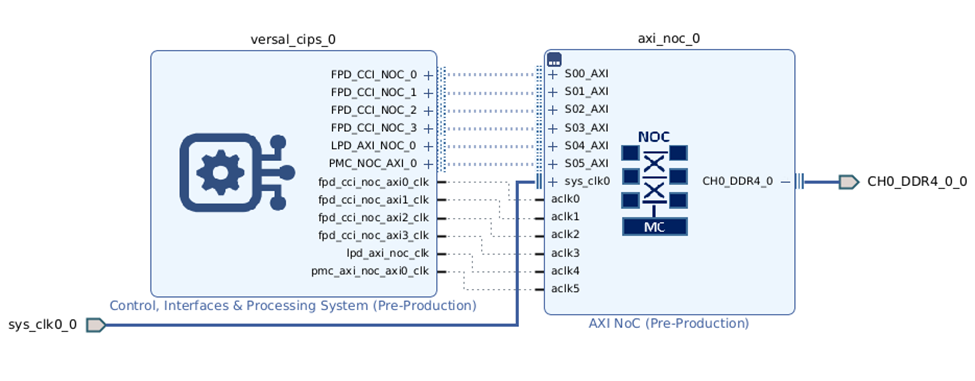

8. 最后,连接CIPS的hsm1_ref_clk端口到DDRMC的sys_clk0端口