设计、编译、交付,轻松搞定。更快更高效。

Vivado 设计套件提供经过优化的设计流程,让传统 FPGA 开发人员能够加快完成 Versal 自适应 SoC 设计。

面向硬件开发人员的精简设计流程

顶层 RTL 流程

通过使用顶层 RTL,用户能够像配置片上网络和收发器一样配置关键的硬核 IP,从而获得类似于传统 FPGA 设计的体验。

快速编译

全新“高级流程”实现算法融合了分层设计优化和并行执行机制,可有效解决拥塞、可布线性和运行时等问题。

优先启动处理子系统

优先启动处理子系统以加快操作系统初始化,同时支持多种启动顺序,并且可选择关闭可编程逻辑并在需要时重新开启。

满足 FMAX 目标

Versal 自适应 SoC 虽然采用经过实践检验的 FPGA 方法,但开创了一种全新的系统设计范式。Versal 架构和 Vivado 设计套件中的以下功能有助于实现时序收敛:

优化的编译流程,旨在减少布线拥塞

时钟区域自动校准功能,旨在充分消减时钟偏移

全新时钟缓冲器技术,旨在实现时钟偏移消减目标

经过增强的裸片间连接能力,适用于基于 SSIT 的器件

借助 Vivado 工具中的全新增强功能以及内置芯片功能,实现自动化和用户控制,从而加快完成时序收敛。

快速编译和灵活启动

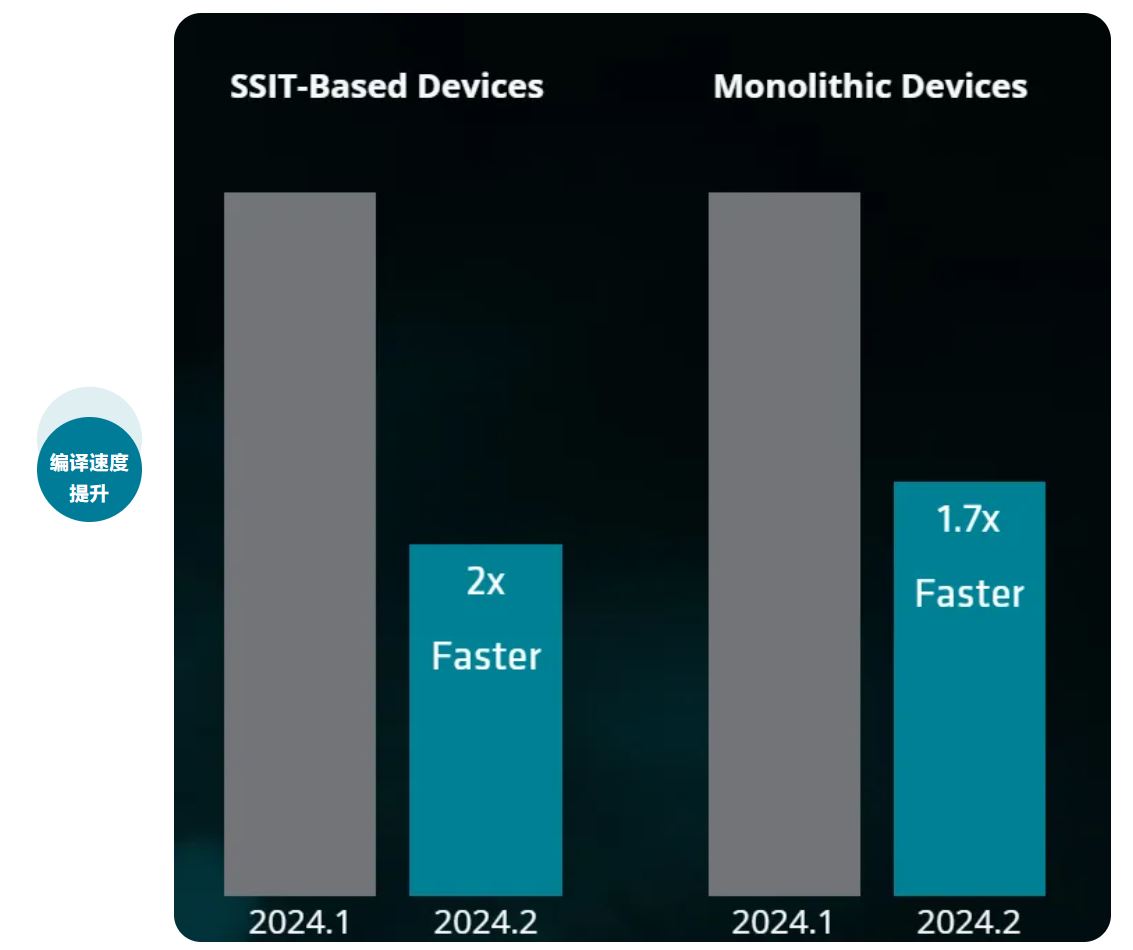

编译速度提升最高可达 2 倍1,2

Versal 自适应 SoC 提供更多逻辑资源和硬核 IP,可胜任更为复杂的设计。然而,更为复杂的设计可能需要更长的编译时间。Vivado 设计套件现推出“高级流程”,在每个实现阶段都进行了优化改进,与先前版本相比,编译速度提升最高可达 2 倍:

自动分区以实现并行布局布线 布局更智能以充分减少拥塞 高级布线算法加快时序收敛

灵活的处理器启动方式

对于需要快速启动操作系统、严格控制电源排序、动态重配置 PL 而不中断软件运行时的应用,Vivado Design Suite 提供了多个选项,支持将处理系统配置为优先启动。全新的分段配置流程:

优先启动处理器、存储器和操作系统

将 PL 配置推迟到后续阶段

在运行时通过 Linux® 或 U-Boot 交付 PL PDI(配置文件)

分段配置在 2024.2 版中作为抢先体验( EA )功能推出。更多详情,可参阅 GitHub 教程。

顶层 RTL 流程

对于 Versal 自适应 SoC,硬件开发人员可以使用 IP Integrator 通过基于模块的系统方法来映射设计,或者继续使用顶层 RTL 以便通过以下两项新功能轻松迁移上一代 FPGA 设计:

模块化 NoC 流程采用系统级方法,支持通过 RTL 和 IP integrator 环境进行例化处理,从而简化设计输入。

新增的 Versal 收发器向导提供基于 GT 原语创建的 RTL 封装,支持进行基本的自定义设置。

在 Versal 自适应 SoC 设计流程中,IP integrator 仍可用于构建各种 IP 块,而通过顶层 RTL 流程可灵活导入具有复杂拓扑的设计。

下一步

如果您希望:

获取培训课程、Versal 自适应 SoC 设计流程中心、快速入门教程和视频、第一代 Versal 自适应 SoC 及第二代 Versal 自适应 SoC 介绍

下载最新 Vivado 2024.2 版,获取全新推出的功能

下载 Power Design Manager 2024.2 版,确保获得 UltraScale+ 和 Versal 器件的准确功耗数据

敬请访问官网专区

1.基于 AMD 于 2024 年 12 月进行的一项测试,该测试分别使用 Vivado Design Suite 2024.2 和 Vivado Design Suite 2024.1 处理 124 个 Versal 堆叠芯片互联 (SSI) 技术器件的设计工作,以衡量平均编译时间(小时/分钟)。测出的编译时间因器件、设计、配置和其他因素而异。(VIV-011)

2.基于 AMD 于 2024 年 12 月进行的一项测试,该测试分别使用 Vivado Design Suite 2024.2 和 Vivado Design Suite 2024.1 处理 151 个 Versal 单片器件的设计工作,以衡量平均编译时间(小时/分钟)。测出的编译时间因器件、设计、配置和其他因素而异。(VIV-010)