硬件加速和基于FPGA的原型设计诞生于1980年代中期,开发者将当时初露头角的现场可编程门阵列(FPGA)率先应用于硅前设计的原型验证,由此催生了一种全新的验证工具,打破了软件仿真的主导局面。

最初,硬件加速的实现过程不仅复杂且依赖专业知识,因此发展受限。然而,在简化启动和调试方面,通过软件与架构层面的持续优化与创新,推动了这项技术的发展。从1990年代中期到21世纪初,硬件加速逐渐成熟,成为验证复杂处理器和显卡设计的关键方法。在这一时期,在线硬件加速(ICE)兴起,它将被测设计(DUT)部署在预期的物理目标系统中,这种方法与FPGA原型设计密切相关。

硬件加速与FPGA原型设计的融合,形成了硬件辅助验证(HAV)平台,标志着下一阶段的到来。HAV利用硬件加速实现了大规模设计的快速启动和同步系统的全面调试——一个模块中的一步操作会触发整个设计的协同推进。FPGA原型设计则更注重执行速度,能够实现与最终设计非常接近的复杂异步操作。尽管这种方法提高了性能,但需要更长的启动周期。与此同时,分割工具的进步使得大规模原型的开发突破了十亿门的门槛。

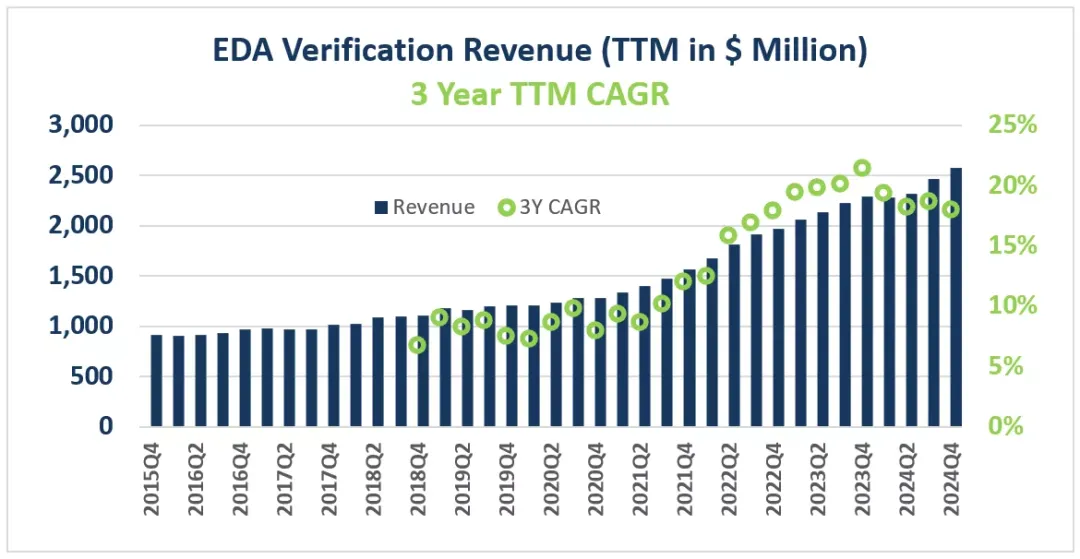

尽管HAV在2010年代中期之前发展相对停滞,但自2018年起,HAV的采用率大幅上升,总收入迅速增长,标志着HAV开始复兴。如下图所示,在整体验证收入中,HAV是目前占比最大的组成部分。

EDA验证收入增长(来源:ESDA)

推动HAV增长的因素

HAV增长的主要推动力在于当今片上系统(SoC)的硬件和软件组件日益复杂。随着硬件设计规模的扩大,完成全面验证所需的周期数相应增加。软件的日益密集也迫使进行更多测试,以确保功能和性能。将设计复杂度和软件复杂度(即验证周期数)分别绘制在x轴和y轴上,得出的面积即代表总验证工作量。总验证工作量在两个维度快速增长,凸显出对HAV解决方案日益迫切的需求。

另一个同样重要的增长推动力在于新型AI硬件的根本特性。与擅长运行软件程序的传统中央处理器(CPU)不同,AI加速器基于专为大规模并行计算设计的架构,以满足机器学习算法的处理需求。

CPU与专用AI加速器之间的本质区别源于它们不同的设计理念和目标工作负载。CPU是通用计算的主力,针对指令顺序处理进行了优化,尤其擅长运行以逐步执行任务为主的软件应用程序。尽管如今的CPU集成了多个内核以实现并行处理,但其固有架构仍面向串行运算,在应对当前人工智能需求时存在扩展瓶颈。最尖端的服务器CPU,如AMD的EPYC系列就采用了这种设计,内核数高达192个,但在面对AI需求时仍显不足。

相比之下,AI加速器(包括图形处理单元GPU、张量处理单元TPU和定制专用集成电路ASIC)在架构上专为执行AI算法而设计,能够同时处理大型语言模型(LLM)中数以千亿计的参数。AI加速器的核心优势在于能够同时执行大量计算,特别是神经网络计算中至关重要的矩阵乘法和卷积操作,需要并行处理海量数据,而CPU通常难以胜任。

例如,英伟达的顶尖产品Blackwell GB202 GPU,拥有24,576个计算内核,就体现了这种范式转变。然而,AI加速器的真正优势在于其集成到大规模系统中的能力。CPU的扩展受制于软件和架构,而AI加速器则不同,可以通过高带宽技术互连,形成统一的处理中心。英伟达的GB200 NVL72集成了72个Blackwell GPU和36个Grace CPU,有效地将单个系统内的AI内核总数推高至一百万个以上。这种大规模并行处理能力对于运行复杂的AI模型至关重要,因为需要同时处理海量数据集并执行复杂计算。

尽管存在架构差异,但CPU和AI加速器都需要通过执行软件工作任务,进行严格的硅前验证。此过程涉及运行业界基准程序和最终用户应用程序;AI加速器,还需要运行LLM。此外,内核间的协同一致性测试进一步扩展了验证范围。以RISC-V为例,验证ISA扩展会进一步增加CPU硅前验证的复杂性。由于每天需要多次迭代执行软件工作任务,因此为完成全面测试,需要数千万亿个验证周期。

AI处理器的验证

在验证AI处理器时,一个独特挑战在于AI模型具有双重运行模式:训练和推理。训练需要处理海量数据,以对深嵌在多层深度神经网络内的网络参数进行微调。该计算密集型阶段可能持续数周甚至数月,要求达到每秒数PFLOP吞吐量和TB级内存带宽。推理阶段由于数据集较小,因此对原始计算的要求不高,但更加注重低延迟,以便在严格的能耗和成本约束下实现实时输出。

这些运算的体量惊人。验证AI硬件加速器和复杂计算集群(其中协同一致性至关重要)时,通常需要数千万亿个验证周期,以确保性能、能效、准确性和可靠性达到预期。如此庞大的测试量远远超出了软件仿真工具的能力,在面对AI工作任务的复杂性和并行性时也显得力不从心。

导致千万亿个验证周期需求的主要因素

HAV化解困局

随着AI模型越来越复杂、工作负载规模愈加庞大,部署HAV平台势在必行。

硬件加速器和FPGA原型提供了周期精确、运行高速的环境运行这些工作负载,使开发者能够在硅前阶段识别并修正设计缺陷。

HAV持续增长的原因显而易见:AI的兴起引发了单靠软件仿真已无法应对的验证环节瓶颈。在通过实际工作负载来验证复杂的AI硬件时,面对速度、容量和可扩展性的高要求,软件仿真和HAV平台的角色已然发生改变。尽管软件仿真凭借强大的调试能力,在IP、模块和子系统设计的验证中仍不可替代,但HAV平台已经成为全系统、Multi-Die和芯粒(即系统之系统,SoS)验证的基石,可实现大规模的硅前验证。

展望未来

推动HAV崛起的几个关键趋势,将继续促进HAV的普及。首先,AI模型日益复杂,新型架构(尤其是在内存和通信接口方面快速演进的架构)不断涌现,将需要更强大且可扩展的验证工具。其次,AI系统对能效和软件安全日益重视,将推动HAV平台的部署,用于在实际工作负载中对峰值和平均功耗进行精确分析并开展全面的安全验证。再者,AI被广泛应用于自动驾驶、医疗健康等各种场景,针对不同领域的定制化验证方法将变得愈发重要。

为了满足这些不断变化的需求,HAV平台必须采用多项关键创新。AI分析工具将提升错误检测和根本原因分析能力,从而显著提高验证效率。基于云的硬件加速和原型验证将提供可扩展性和可访问性,使设计工作流程更加灵活。标准化的验证方法和基准将促进行业协作与互操作性。在计算、AI训练、边缘AI、汽车、消费电子及有线/无线应用领域,由于验证设置各不相同,模块化验证对于管理超过600亿门级别的超大设计和复杂的SoS配置至关重要。此外,硬件加速和原型验证的融合将带来更顺畅和一体化的验证流程。

总之,AI的快速发展及软件开发日益增长的复杂性与成本,直接促成了硬件辅助验证平台的复兴。由于AI硬件加速器在大规模并行、高算力工作任务及性能与功耗方面的严苛要求,HAV已成为设计过程中的关键环节。

随着AI不断发展并全面渗透现代科技,HAV在确保性能、低功耗、准确性、可靠性和软件安全方面的作用将愈发重要。通过持续创新并适应AI的发展趋势,HAV平台将在下一代硬件开发中继续发挥关键作用。

文章来源:新思科技