作者:于兆杰,来源:亚科鸿禹

“第三届芯粒开发者大会”于7月15日在无锡成功举办,亚科鸿禹团队作为成熟的前端功能验证EDA工具及解决方案供应商受邀参与大会,与上下游企业签署共建芯粒库战略协议,共同推动我国芯粒技术与产业高质量发展,致力于推动国产半导体领域创新突破,并应大会“芯粒测试与验证”分论坛邀请,发表题为“Hybrid虚拟原型在Chiplet芯片验证中的应用”主旨演讲。

芯粒系统是将多个预先制造好的芯粒(Chiplet)集成在一起的系统。这些芯粒可能具有不同的功能,例如计算单元、存储单元、通信接口等,而芯粒系统中的芯粒数量在某些高端应用中可能达到数十个之多。而在芯粒系统架构设计之初的系统级验证显得尤为重要。

FPGA虚拟原型是利用FPGA构建的一种虚拟的系统模型,它可以在芯粒系统设计的早期阶段,在没有物理芯粒的情况下,对芯粒系统进行功能和性能的模拟验证。通过软件工具和硬件描述语言,可以在FPGA上创建芯粒系统的虚拟模型,模拟各个芯粒之间的交互以及整个系统的运行情况。对于不同的芯粒互联架构,根据功能、性能等指标的数据对比,选择最优的设计方案。

基于FPGA的虚拟原型系统是结合了底层逻辑端硬件和上层应用软件,通过软硬件协同验证的方式加速芯粒系统的嵌入式软件开发和不同功能芯粒的接口相关的逻辑开发。虚拟原型系统结合了处理器模拟器和硬件构建块的各种芯粒的功能模型,为软件开发人员和系统架构师提供硬件的抽象可执行表示。

虚拟原型的软硬件协同验证系统具有以下三个特点:

虚拟化:支持Qemu模拟器模拟基础的处理器系统及各种功能外设。

自动化:通过完善的脚本实现编译、启动系统等。

可扩展:支持扩展开发常用的CPU外围设备以及芯粒中集成的各种功能模块

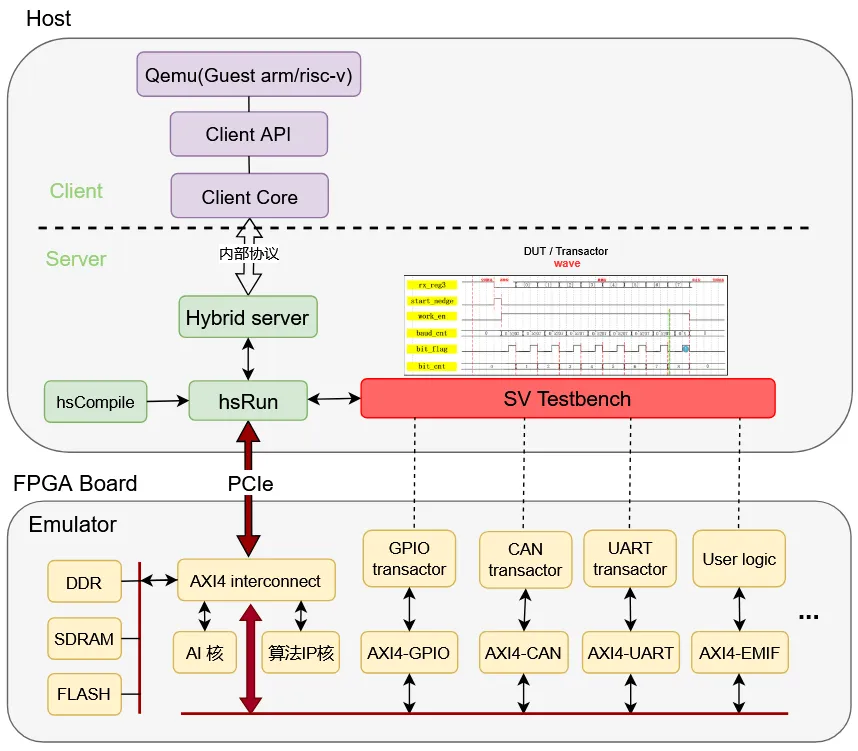

借助亚科鸿禹的“FPGA的软硬件协同验证系统”来进一步了解其构成。系统架构参考如下图:

最底层是FPGA硬件,包括了FPGA逻辑侧实现的常用的高速以及低速外设接口模型,比如GPIO/CAN/UART/UCIe/PCIe/Ethernet等模块;另外还可以有用户自定义的算法IP核,比如各类加速器算法模块和GPU/GPGPU/NPU等,同时还支持HBM、DDR、SDRAM和FLASH的访存模块,为用户验证芯粒系统提供了基础的硬件模块。

上层是软件层,软件通过PCIe接口访问硬件逻辑,软件层中主要分为Server端和Client端,Server端包含了亚科鸿禹编译软件hsCompile执行Runtime的软件hsRun以及Hybrid server。其中:

hsRun对接最底层硬件,包括对接AXI4和AMBA等最底层的硬件总线,同时hsRun提供了对硬件FPGA等的DB下载和reset等的控制功能。 hsCompile利用Verilog设计文件生成DataBase文件,这里的DataBase中包含了FPGA的bit文件,通过hsRun下载到FPGA中。 SV Testbench是FPGA的测试文件,运行在Host端,同时主机端可通过Testbench和hsRun生成FPGA逻辑端的信号波形文件,通过查看信号波形调试逻辑。 Hybrid server为上层Client提供了特定的外设等的功能,Client把Hybrid server当成芯粒中需要集成的模块来访问,Hybrid server对底层的AXI等的接口进一步封装,给上层Client提供高层次的接口和功能。 Client主要在底层访问Hybrid server接口,在上层通过Qemu模拟器启动的Linux Guest,软件端利用Qemu模拟器的功能,在Guest中可同时使用Qemu模拟器模拟的CPU、DMA和底层Hybrid server提供的UART、CAN等逻辑端实现的功能。通过使用Qemu模拟功能和FPGA逻辑端实现的DUT达到软件和硬件协同验证的效果。

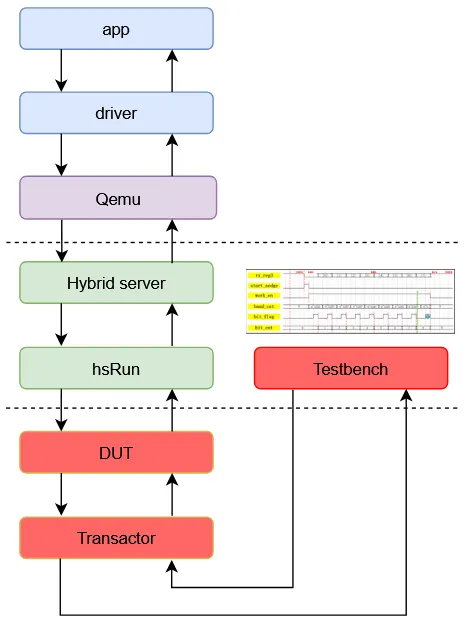

结合高层软件和底层逻辑的这种协同仿真验证,参考下图的数据流程:

当我们验证一个芯粒系统架构和功能时,在开发FPGA底层逻辑的同时,可以对上层嵌入式app、driver和芯粒相关的软件进行开发,并且这些软件在开发时就可以和逻辑端FPGA一起进行联调。这种协同开发验证的功能有:

提早开发嵌入式软件,加快软件开发进度。 支持软件虚拟化,在早期可以利用Qemu模拟器模拟的芯粒部分功能暂时替代FPGA逻辑端还没实现的功能。 软硬件联调能提早暴露出整个软件设计和FPGA逻辑端设计中的Bug和不足。 支持传统的在主机中抓取波形信号。 扩展方便,底层FPGA逻辑端扩展的功能,通过上层软件可以快速的验证正确性。 确定性,在物理硬件上重现间歇性问题或复杂的时序相关问题是困难的。相反,软硬件协同加速嵌入式软件开发平台以测试用例的可重复性形式提供确定性,用户将一次又一次地获得完全相同的行为。 综上,一个芯粒的研发验证需要整体的验证和核查、优化和权衡分析、确保兼容性和互操作性,hybrid FPGA软硬件协同验证系统为系统整体的验证、优化和互操作性提供了一套较为完整的解决方案。

值得注意的是,虽然FPGA虚拟原型能够模拟芯粒系统的大部分功能,但在某些高精度的模拟场景下,如模拟某些模拟电路的行为或者非常精确的信号物理特性时,还存在一定的局限性。目前,模型的精度只能达到一定的水平,与实际物理系统可能存在一定的偏差。另外,FPGA的资源是有限的,当模拟非常大规模的芯粒系统时,可能会面临资源不足的问题。例如,在模拟一个包含大量高复杂度芯粒的超级计算机芯粒系统时,FPGA的逻辑资源、存储资源等可能无法满足需求,从而影响虚拟原型的完整性和准确性。