文章来源:OpenFPGA

面对数据中心网络性能瓶颈,Open-NIC 项目由 Xilinx 推出,提供了一个开源 FPGA-based NIC 平台,帮助开发者与研究者轻松实现硬件网络加速与原型验证。本文将为你深入解读 Open-NIC 的架构、组件与应用场景。

什么是 Open-NIC?

Open-NIC 是由 AMD-Xilinx 推出的开源 NIC 平台,主要面向 FPGA 开发者与网络应用研究者,目标是打造便于接入的硬件网络原型架构。其支持按需集成用户逻辑,加速网络相关应用的开发。

三大核心组件一览

Open-NIC 项目包含三个关键模块:

Open-NIC Shell(硬件 shell)

https://github.com/Xilinx/open-nic-shell.git

提供 RTL 设计,可用于几款 Alveo UltraScale+ FPGA 卡(如 U50、U55C、U280 等)

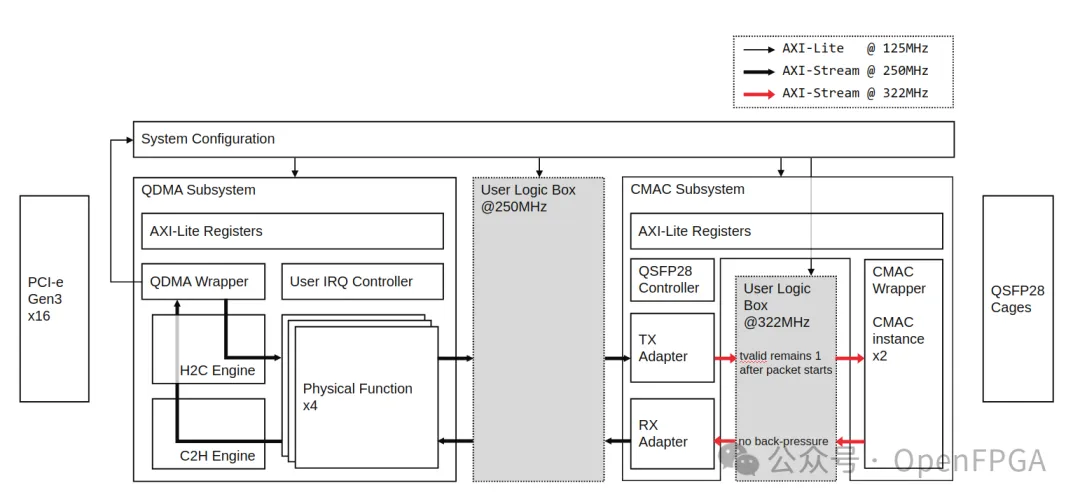

支持 4 个 PCIe PF(物理功能)与 2 个 100GbE 网络端口,提供标准 QDMA 与 CMAC 接口,还预留了用户逻辑插槽,方便功能定制

Open-NIC Driver(Linux 驱动)

https://github.com/Xilinx/open-nic-driver.git

提供 Linux 内核驱动,支持多 PF、多 TX/RX 队列。支持的操作环境包括 Ubuntu 18.04、20.04、22.04

提供基本的网络设备接口,可进行 loopback 测试、ethtool 查询等实践操作

Open-NIC DPDK 驱动

https://github.com/Xilinx/open-nic-dpdk.git

包含针对 DPDK 的 Patch 文件与构建指南,将 Open-NIC 支持整合到 DPDK 框架,适用于 Ubuntu 等平台。

项目亮点与技术价值

开源开放,适配多种硬件: 使用 Apache-2.0 或 GPL-2.0 授权

硬件加速路径清晰: Shell 内部划分 QDMA、CMAC 与用户逻辑区块,设计结构清晰,便于集成自定义网络处理模块

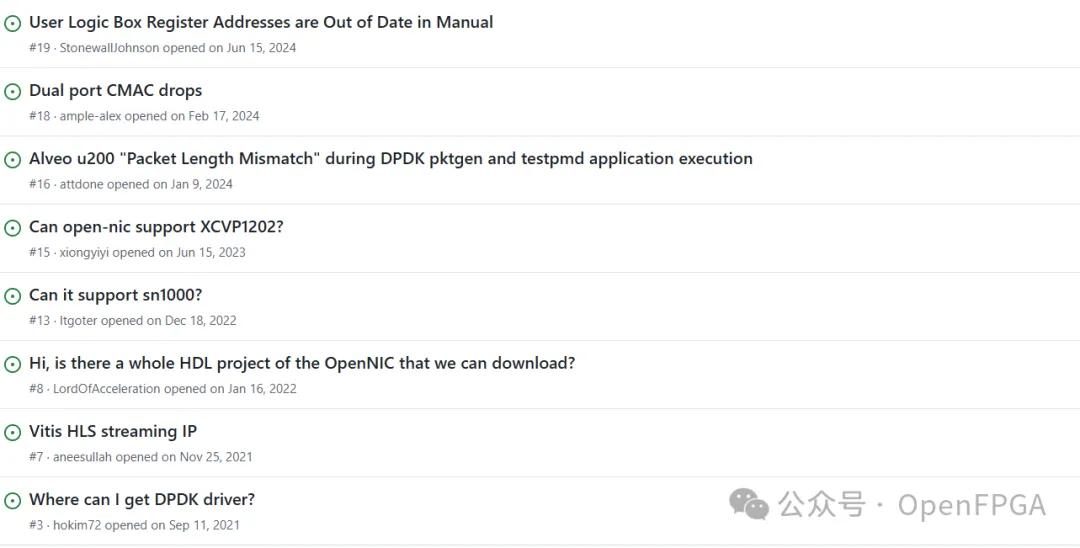

社区活跃,持续优化中: 项目 issues 显示用户积极反馈,涵盖 SR-IOV 支持、链路接收异常、MAC 配置、U-series FPGA 兼容性等多个方向

典型应用与开发流程

推荐入门路径(以 Alveo U55C 为例):

下载三个仓库:open-nic-shell、open-nic-driver、open-nic-dpdk;

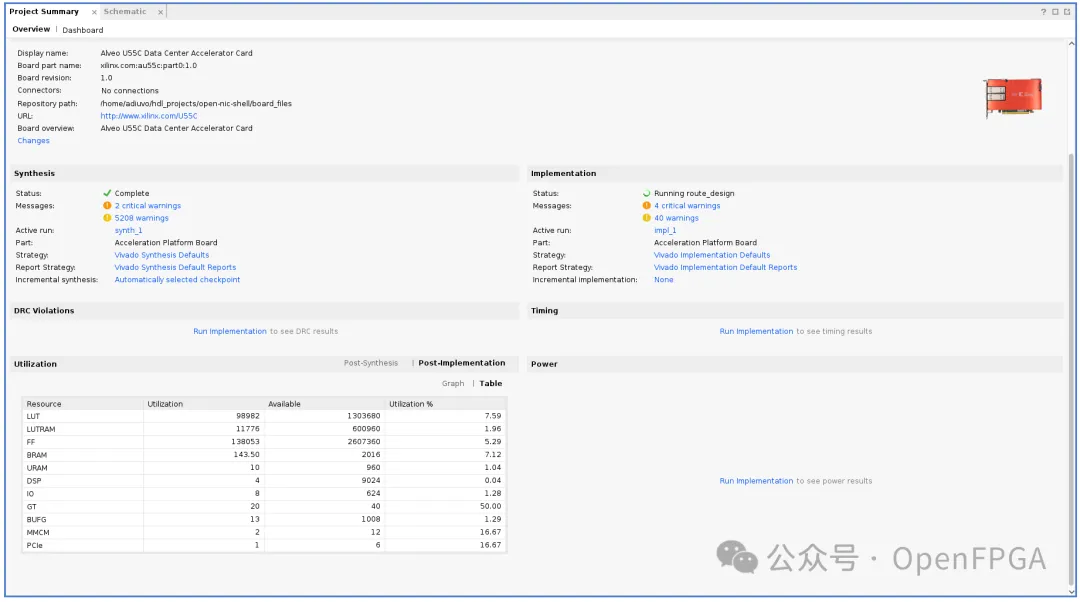

使用 Vivado 2022.2(OpenNIC 支持的最新版本),运行以下命令来构建 shell

vivado -mode gui -source build.tcl -tclargs -board au55c -synth_ip 0

这将创建包含两个user boxes的 shell,第一个user boxes的主频为 250MHz,第二个user boxes的主频为 322MHz。由于 Alveo 卡将 CMAC 和 PCIe 实现为硬 IP,因此 shell 的资源占用率非常低。

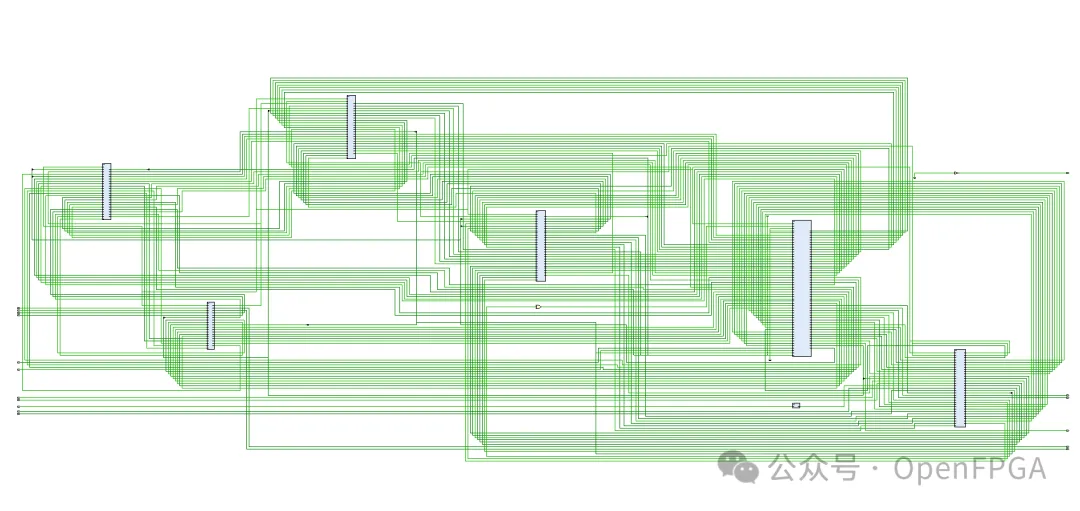

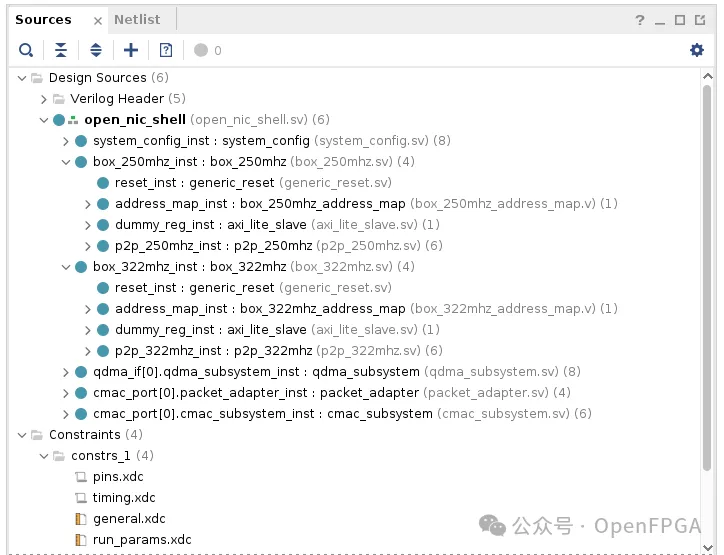

一旦在 Vivado 中创建设计,我们就可以探索该设计,在源视图中,我们可以清楚地看到自定义添加的两个user boxes和插入的逻辑以完成基础设计。

场景示例:

网络协议硬件加速:如定制过滤、转发逻辑等;

数据中心性能验证平台:大流量与并发场景测试;

教学与研究用途:网络架构、硬件加速、FPGA 教学平台。

总结

Xilinx Open-NIC 项目通过 shell + 驱动 + DPDK 三位一体的方案,为硬件网络加速提供了开源、灵活、高性能的路径。尤其适合研究者、开发者探索 FPGA 与 SmartNIC 结合的可能性。