AMD 自适应计算文档按一组标准设计进程进行组织,以便帮助您查找当前开发任务相关的内容。您可以在设计中心页面上访问 AMD Versal™ 自适应 SoC 设计进程。您还可以使用设计流程助手来更深入了解设计流程,并找到特定于预期设计需求的内容。本文档涵盖了以下设计进程:

嵌入式软件开发:基于硬件平台来创建软件平台,并使用嵌入式 CPU 开发应用代码。还涵盖 XRT 和计算图 API。本文档中适用于此设计进程的主题包括:

- 第 2 章:在嵌入式设计中使用 MicroBlaze V 处理器

硬件、IP 和平台开发:为硬件平台创建 PL IP 块、创建 PL 内核、功能仿真以及评估 AMD Vivado™ 时序收敛、资源使用情况和功耗收敛。还涉及为系统集成开发硬件平台。本文档中适用于此设计进程的主题包括:

- 第 3 章:含存储器 IP 核的设计

- 第 4 章:IP integrator 中的复位和时钟拓扑结构

器件工具流程概述

AMD Vivado™ 工具基于处理器提供了特定的编程流程。Vivado IDE 使用 IP integrator 搭配图形化连接屏幕以指定器件、选择外设和配置硬件设置。

您可使用 IP integrator 捕获硬件平台信息并导出 XML 格式的应用程序,搭配其他数据文件来为 AMD 处理器开发设计。各软件设计工具使用 XML 来执行以下任务。

创建并配置板级支持包( BSP )库

推断编译器选项

对处理器逻辑( PL )进行编程

定义 JTAG 设置

自动执行需要有关硬件的信息的其他操作

AMD MicroBlaze™ V 嵌入式处理器是精简指令集计算机( RISC )核,专为在 AMD 现场可编程门阵列( FPGA 和自适应 SoC )中实现而优化。该核基于 RISC-V 开源指令集架构。

要创建嵌入式 MicroBlaze V 处理器设计,请参阅第 2 章:在嵌入式设计中使用 MicroBlaze V 处理器,以便了解如何使用 IP integrator 和其他 AMD 工具。如需了解更多处理器信息,请参阅《MicroBlaze V 处理器参考指南》( UG1629 )。

AMD 提供了设计工具,用于为 AMD 处理器开发和调试软件应用,包括但不限于: 软件 IDE 基于 GNU 的编译器工具链 调试工具 这些工具支持您开发无需操作系统的裸机应用和用于基于开源 Linux 操作系统的应用。

AMD 提供硬件设计和软件开发集成,并支持集成流程向下延伸至 AMD Vitis™ 软件平台。Vitis 是独立产品,可从 AMD 网站下载。如需了解有关该工具使用方法的更多信息,请参阅《Vitis 统一软件平台文档》。

注释:MicroBlaze V 要求使用 Vitis Unified IDE。

在嵌入式设计中使用 MicroBlaze V 处理器

AMD Vivado™ IDE IP integrator 是一款强大的工具,支持您将基于处理器的系统缝合在一起。

MicroBlaze V 嵌入式处理器是专为在 AMD 现场可编程门阵列( FPGA )中实现而优化的精简指令集计算机( RISC )。

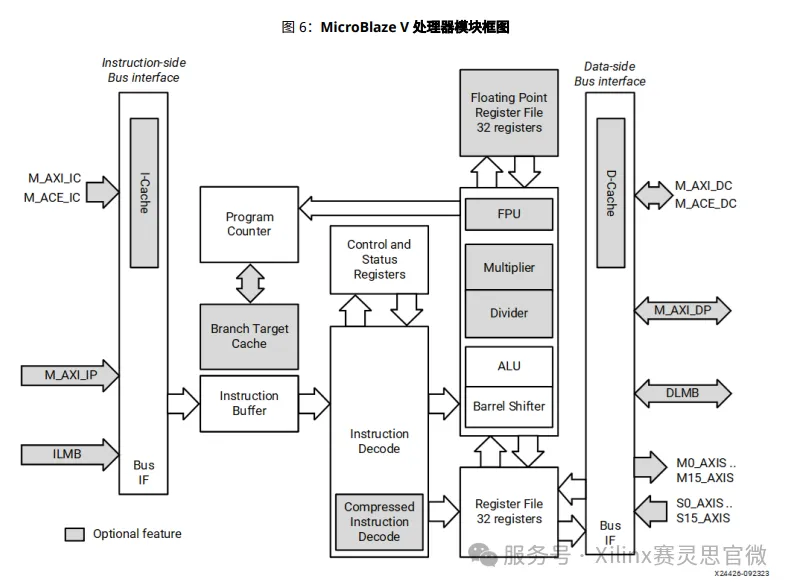

下图显示了该 MicroBlaze V 核的功能模块框图。

MicroBlaze V 处理器高度可配置。您可按设计所需选择一组特定的功能特性。固定的处理器功能集包括: 32 个 32 位或 64 位通用寄存器 32 位指令字 32 位地址总线,可扩展至 64 位 单发射流水线

除这些固定功能特性外,MicroBlaze V 处理器还包含参数化值,支持有选择地启用附加功能。

如需了解更多信息,请参阅《MicroBlaze V 处理器参考指南》( UG1629 )。

根据用户要求,MicroBlaze V 可作为 32 位处理器或 64 位处理器来实现。一般来说,除非无法满足特定要求,否则 AMD 建议您选择 32 位处理器实现。64 位处理器会将通用寄存器扩展到 64 位,提供指令用于处理 64 位数据,并能使用最多 64 位地址对指令和数据进行透明化寻址。

另请参阅《Triple Modular Redundancy( TMR )LogiCORE IP 产品指南》( PG268 ),其中提供了适用于 AMD 器件的软核错误检测、纠正和恢复。本指南描述了该解决方案所包含的 IP 核,并解释了各种典型用例。

获取完整版《MicroBlaze V 处理器嵌入式设计用户指南》请扫描二维码进行下载