实现 GPU 与 CPU I/O 扩展与安全保障

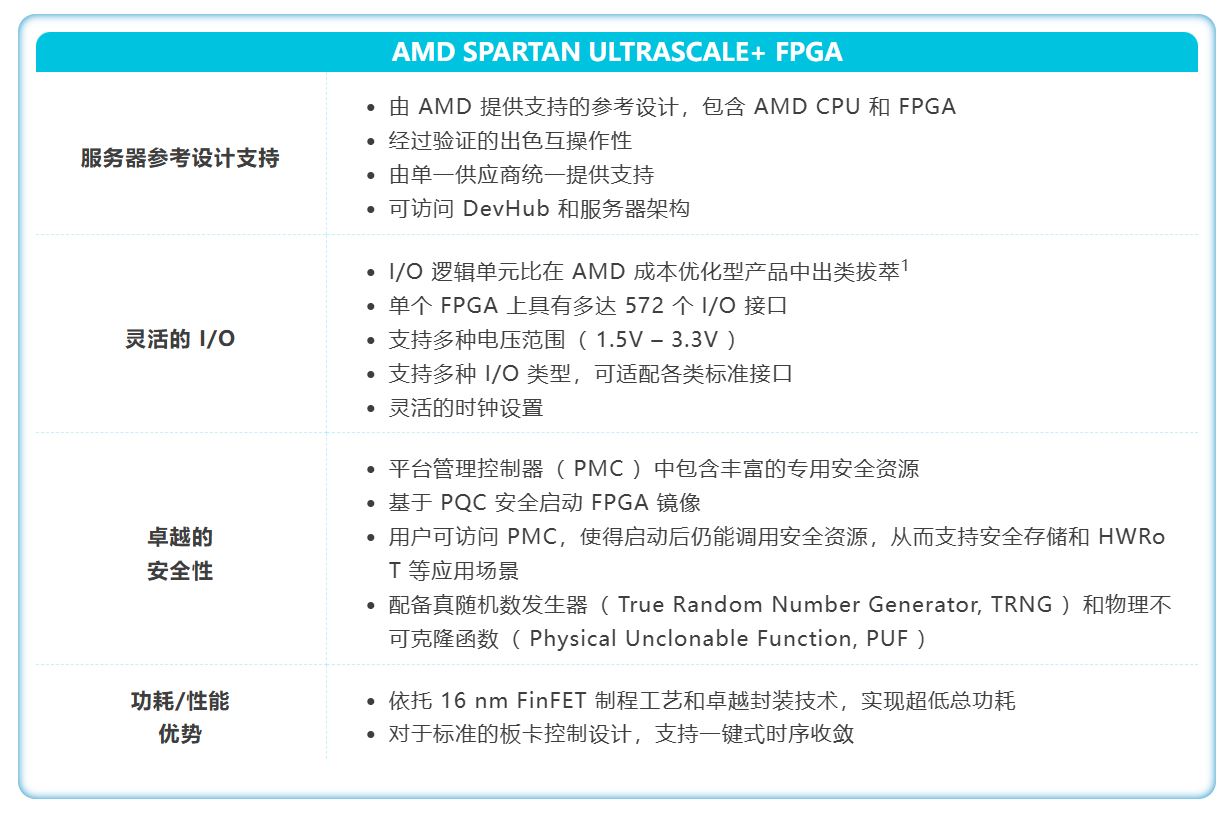

如今,数据中心服务器市场的竞争日益激烈。服务器制造商可采用的底层计算技术逐渐趋同,这意味着性能已成为行业标配。为打造差异化优势并在市场竞争中脱颖而出,原始设计制造商( ODM )和原始设备制造商( OEM )开始集成更为先进的功能特性。高级安全防护、实时监控、网络连接、能效管理等功能正成为左右采购决策的关键因素。目前,绝大多数服务器都借助 FPGA 来提升主机处理器主板( HPM )和服务器控制模块( SCM )的智能化水平,从而实现差异化优势。AMD Spartan™ UltraScale+™ FPGA 不仅采用后量子密码学( PQC )实现卓越安全防护,而且其 I/O 与可编程逻辑资源比在 AMD 成本优化型产品中出类拔萃1,同时可与 AMD EPYC(霄龙)服务器 CPU 深度集成。凭借这些显著优势,该系列 FPGA 可为新一代服务器设计提供强大助力。

主要优势

AMD EPYC(霄龙)处理器参考设计的组成部分

面向 Spartan UltraScale+ FPGA 与 AMD EPYC(霄龙)主机处理器的设计

低风险的主板实现方案

覆盖多种产品的 AMD 技术支持

I/O 效率

整合多种低速信号协议

支持 I2C/SMBus、GPIO 和 UART

充分减少组件连接所需的 I/O 管脚

节省板卡空间

互操作性与开放标准

符合开放计算平台( OCP )规范

IP 已按最新规范完成测试

LTPI IP 可供使用

适配多供应商 x86 平台

FPGA 硬件灵活性

高效利用架构资源

支持现场升级以适配新标准

依托庞大的 IP 目录,快速适应需求变化

集成更多功能

电源监控与控制

系统复位与初始化逻辑

热插拔逻辑

适用于 CPU 和 BMC 的 I/O 扩展器

亮点

采用经过验证的 CPU + FPGA 解决方案,助力加快上市速度

借助基于 Spartan 7 和 Spartan UltraScale+ FPGA 设计的 AMD EPYC(霄龙)HPM 和 SCM 参考平台,缩减运营支出并降低进度风险

通过与同时提供 CPU 和 FPGA 的单一供应商合作,简化技术支持

依托先进的开发环境,实现一键式 FPGA 时序收敛

在设计中融入卓越的安全功能

凭借基于 PQC 的 FPGA 安全启动功能,确保 HPM、SCM 和 BMC 等可编程器件的真实性

可编程逻辑能使用硬件级芯片安全资源,以支持安全存储和 PFR 等应用场景,包括配备真随机数发生器( TRNG )、物理不可克隆函数( PUF )、本地密钥管理系统( LMS )等

出色的连接能力与可扩展的产品系列

I/O 逻辑单元比在 AMD 成本优化型产品中出类拔萃,且全方位支持 3.3V I/O1

50 多款成本优化型器件,支持按需选择合适的器件

多种 PCIe® 连接板卡控制选项

基于 7 系列与 UltraScale+ 产品系列,已经过验证,具有出色的可靠性

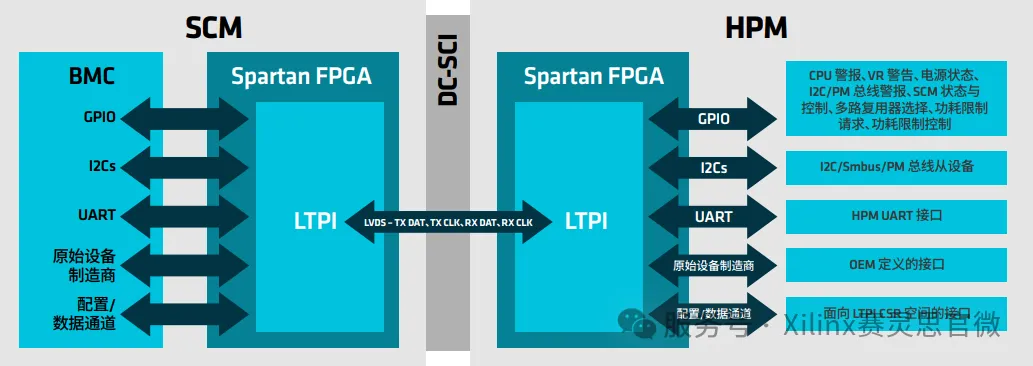

示例服务器 I/O 模块框图

优势

后续步骤

详细了解 AMD 产品优势

如需了解 Spartan UltraScale+ FPGA 芯片及评估板的相关信息,请联系当地的销售代表,或发送电子邮件至 dc-inquiries@amd.com

尾注

1. 基于 AMD 2023 年 12 月的内部分析,对比了 AMD Spartan UltraScale+ FPGA 与前几代 AMD 成本优化型 FPGA 的总 I/O 逻辑单元比。(SUS-001)