作者:Clara An,文章来源:亚科鸿禹

VeriTiger-PT100S是亚科鸿禹全新一代FPGA原型验证平台,搭载最新一代VP1902芯片,具备更大规模的验证容量、更强的系统性能、更灵活的接口扩展,尤其适用于超大规模前沿复杂IC设计的前端全场景验证、高速接口验证及硅前软件开发。本文将详细介绍如何在VeriTiger-PT100S上进行PCIe Gen5验证。

在VP1902上搭载工程,区分以往VU系列,需要关注PS侧相关配置,根据下面章节Versal Premium架构介绍,可以增加对VP系列工程搭建的理解。

Versal Premium 架构介绍

应用处理器(APU)为Arm Cortex-A72:运行于1.5GHz+,用于运行富操作系统(如Linux)和处理复杂的控制平面任务

实时处理器(RPU)为双核Arm Cortex-R5F:运行于600MHz+,用于处理实时、低延迟的任务

平台管理控制器:基于MicroBlaze,独立负责器件的启动、安全、电源管理和监控

外设:包含丰富的标准外设,如GPIO, UART, I2C, SPI, USB等,用于芯片与外部世界的通用通信

这就是传统的FPGA架构部分,但采用了更先进的工艺和架构。

可编程逻辑部分:包含查找表、寄存器、块RAM和分布式RAM,用于实现任何自定义逻辑

DSP切片:大量的DSP48E2切片,提供高吞吐量的定点和高精度浮点运算能力

互连:丰富的布线资源和时钟资源,确保逻辑模块之间以及与其他子系统的高效连接

这是Versal Premium区别于其他系列最显著的地方,它通过硬核IP提供了无可比拟的带宽和能效。

多速率以太网MAC(MRMAC)提供高性能、低延迟的以太网端口,支持广泛的自定义配置和统计信息收集功能。其支持的配置包括:1x100GE、2x50GE、1x40GE、4x25GE和4x10GE。600G信道化多速率以太网子系统(DCMAC)可提供高达600G的以太网带宽,支持包括1x400GE、3x200GE和6x100GE在内的多种速率配置。该DCMAC模块可处理以太网MAC、PCS和FEC的所有协议相关功能,包括握手、同步和差错校验。同时,它还为报文数据提供了分段式AXI4-Stream接口,并为统计管理提供了AXI4-Lite接口。集成的DDR4内存控制器通过片上网络互连进行连接。该控制器同时支持DDR4和LPDDR4内存接口。

PCI Express® 集成模块是一种高带宽、可扩展且可靠的串行互连解决方案,专用于 AMD Versal 自适应SoC。根据设计所使用的具体Versal自适应SoC型号,该可编程逻辑PCI Express®集成模块可实现PCI Express®基础规范4.0(简称PL PCIE4)或 PCI Express®基础规范5.0(简称PL PCIE5)的特定实施方案。其中PCIe Gen5提供高达128GT/s带宽,是连接主机CPU的最新、最快接口。

Versal Premium采用了先进的片上网络。NoC 是一个分层的、基于数据包的网络,它像城市的高速公路系统一样,横跨整个芯片,连接标量引擎、DDR/HBM控制器、PL接口和 AI Engine。它提供可预测的延迟、高吞吐量和服务质量保证,确保数据能在各个子系统之间无阻塞地流动。没有NoC,这些硬核IP的性能将无法充分发挥。

根据Versal Premium架构详解,可以进一步理解片上系统的硬件架构互连示意图:

Versal Premium PCIe 介绍

在Versal架构中,存在多个物理独立的PCIe控制器,它们位于不同的子系统上,以满足不同的系统集成需求。集成在平台管理系统中的PCIe控制器一般有两种:

位于平台管理控制器区域内的硬核IP,通常在文档中被称为PCIe® in PMC 或 CPM。主要特点:通常作为RC运行,负责平台管理和系统启动。例如Versal器件可以通过这个PCIe接口从主机系统启动。可能支持SR-IOV等功能,用于更复杂的虚拟化场景

位于可编程逻辑中的PCIe控制器,作为硬核IP嵌入在可编程逻辑结构中,在文档中可能被称为 PCIe in PL 或 Integrated Block for PCIe。主要特点:更具灵活性。它可以被配置为RC或EP。与PL中的用户逻辑紧密耦合,可以实现自定义的DMA引擎、加速器内核,并通过AXI接口直接与它们通信。通常支持更高的性能版本(如PCIe Gen4/Gen5),具体取决于器件型号

简单区分为:PMC PCIe: 更像一个“系统服务”角色,用于管理、控制和启动;PL PCIe:更像一个“数据平面”角色,用于实现高性能的数据加速和传输

相较于先前架构中的PCIe集成模块,Versal自适应SoC的PL PCIe模块实现了显著的功能增强。若需将既有设计的PCIe集成模块迁移至Versal自适应SoC的PL PCIe模块,请注意以下要点:

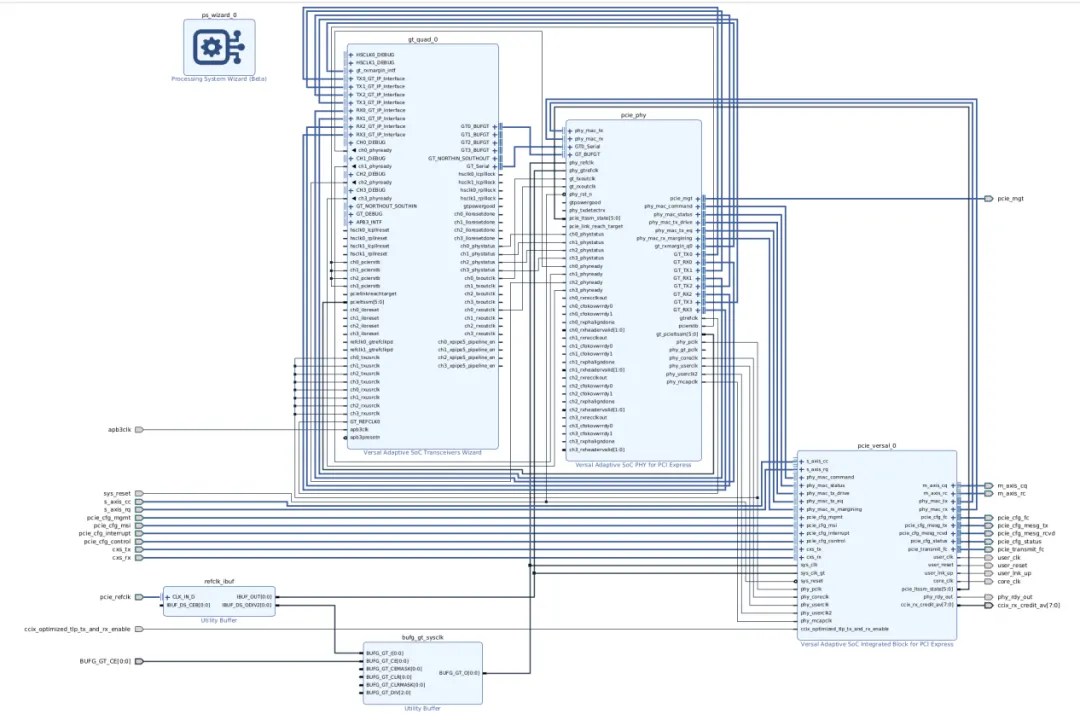

● 目前仅支持基于Vivado IP Integrated Block的模块设计流程,可进行手动或自动连接

● Versal自适应SoC PL PCIe所需的高速收发器与物理层IP模块独立于主功能模块之外

● 应通过PL PCIe模块配置链路速率、位宽及特性参数,可选用自动化流程或手动实例化所需高速收发器与物理层IP

● 推荐通过处理系统内的I/O接口驱动PCIe控制器的基本复位信号(需在CIPS IP中完成配置)

● 需手动映射RQ/RC/CQ/CC数据流接口及边带信号,其映射方式与先前架构的IP实现方式类似

Versal自适应SoC的PCI Express®集成模块所具备的PL PCIe5功能特性,提供了一个高性能PCI Express端口,支持广泛用户自定义配置。

VU系列的19P一般使用的IP为XDMA, PCIe硬核+软核逻辑。XDMA 的全称是Xilinx DMA for PCI Express,它是一个软核IP,集成在FPGA的逻辑资源中,其核心功能是通过PCIe总线实现主机与FPGA之间的直接内存访问。PCIe Hard IP:这是 FPGA 芯片内部硬化的逻辑,负责处理PCIe物理层、数据链路层和事务层的最低层协议,性能最优,资源占用少。XDMA会调用这个硬核。DMA引擎(软核逻辑): 这是XDMA的核心,用FPGA的可编程逻辑实现。它包含多个、独立的DMA通道(Channel),每个通道都可以独立地进行数据搬移。

Versal Premium PCIe取消掉XDMA的IP,只有Integrated Block for PCI Express和Versal Adaptive SoC PCIe PHY 这两种基本IP。Versal Premium 上,使用硬化DMA是处理高带宽数据的首选和推荐方案。

Versal Premium系列“去掉”XDMA,不是一个功能的缺失,而是一次技术的飞跃和定位的升级。它标志着:从“通用可编程”到“特定域硬化”的转变:将高带宽、标准的功能(如DMA)硬化,以释放可编程逻辑用于差异化的算法;从“PCIe 中心”到“网络与计算中心”的转变:数据首要通过高速网络进入,PCIe的角色被重新定义;对更高性能、更低功耗和更优资源利用率的追求:硬化IP在性能、功耗和面积上永远优于软核实现。

PCIe_Gen5 Example 介绍

采用PCIe Gen5是应对现代数据密集型应用对带宽需求爆炸式增长的关键技术决策。可以实现带宽翻倍,消除系统瓶颈,PCIe Gen5的每通道(Lane)单向带宽从Gen4的16GT/s提升至32GT/s。一个x16链路的总双向带宽高达128GB/s。现代高端GPU和AI加速器对数据吞吐量的需求极高,PCIe Gen5确保了CPU与加速器之间、以及多加速器之间的数据通道不会被阻塞,充分发挥其计算潜力。PCIe Gen5 x4的SSD理论带宽可达约16GB/s,是Gen4 SSD的两倍,这对于高性能计算、实时数据分析、大型游戏加载等场景意味着极快的存储访问速度。选择PCIe Gen5的本质是为数据洪流修建一条更宽阔、更高效的高速公路,它直接解决了当前和可预见的未来在人工智能、数据中心、高性能计算和尖端存储等领域出现的I/O性能瓶颈,是构建下一代计算基础设施的基石技术。

后续章节将在VeriTiger-PT100S上进行PCIe Gen5的设置,并实际上板测试。

IP配置

在Vivado中根据VeriTiger-PT100S的FPGA器件新建工程,在此工程下配置PCIe IP。

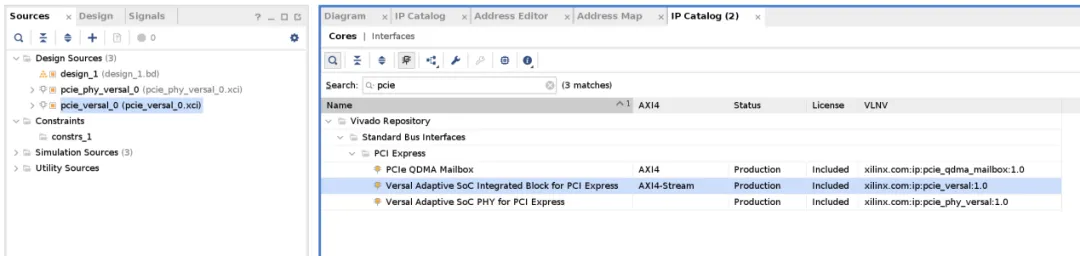

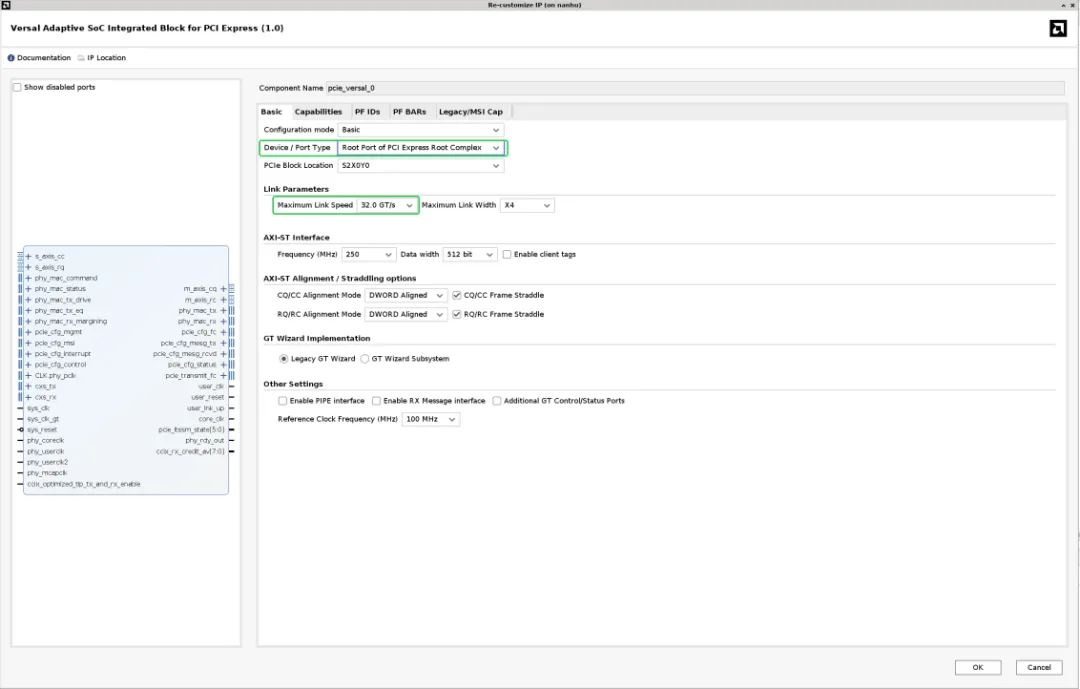

选择IP Integrated Block for PCI Express,进行如下配置:

● Device/Port Type:RC和EP选择

● Maximum Link Speed:PCIe速率选择,可以选择PCIe Gen5 32.0GT/s

● Reference Clock Frenquency:一般选择100Mhz(100Mhz、125Mhz、250Mhz均可以选择)

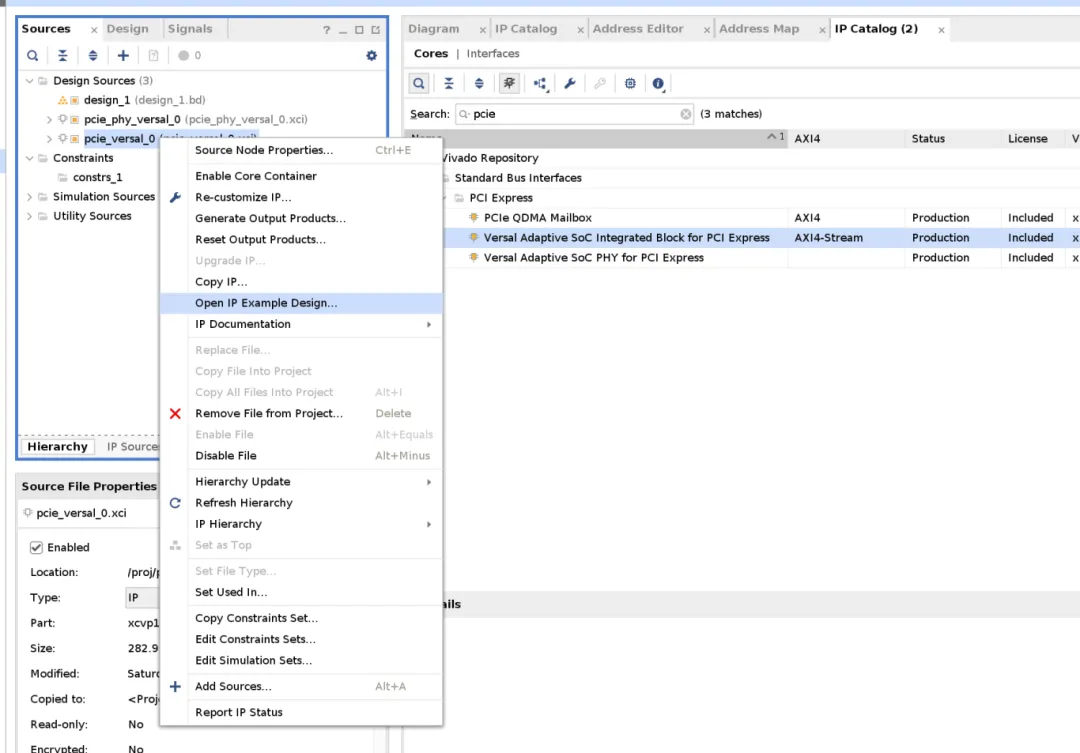

● 其他配置选择默认即可,生成IP后,打开Open IP Example Design,即可生成PCIe相关的Example

将IP设置成EP模式后,生成Example。

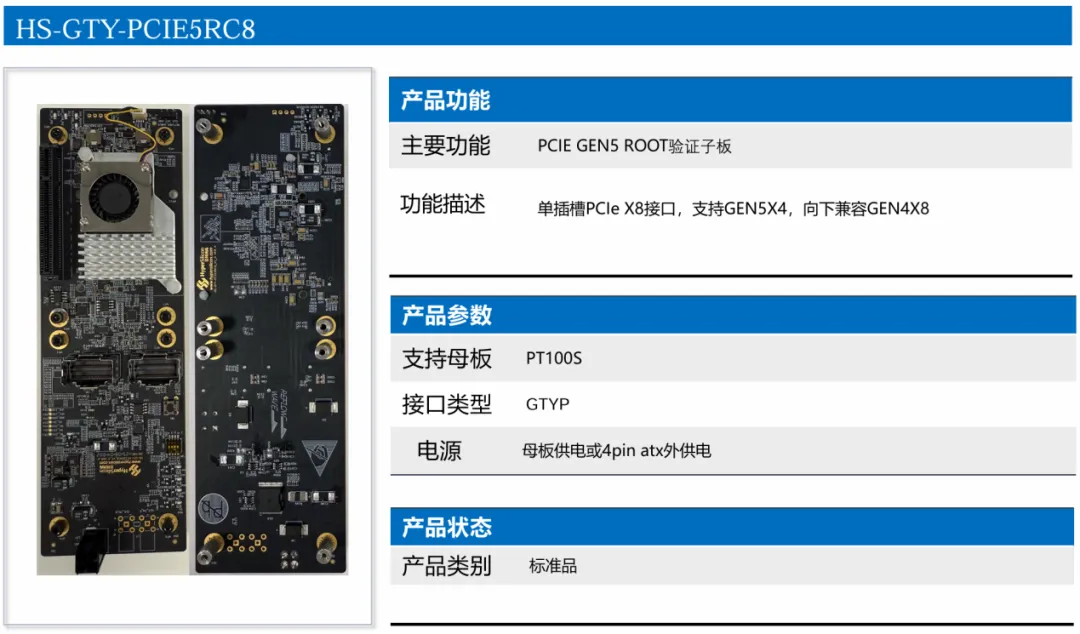

本文介绍的PCIe Gen5工程,环境搭建采用亚科鸿禹自研的母板VeriTiger-PT100S以及配套PCIe Gen5子卡,以下是子卡介绍图。

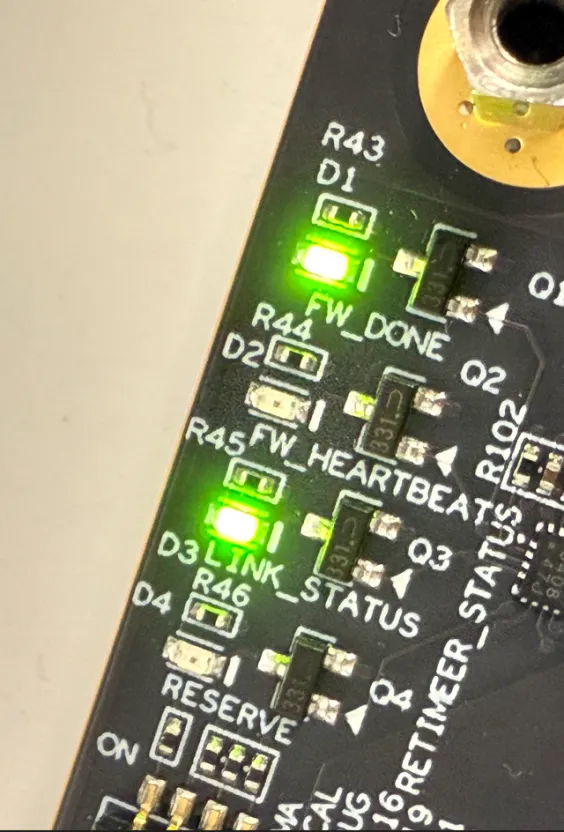

RC8子卡是一张HS-PT100S设备的外接拓展子卡。该子卡提供了一个PCIe X8插槽,为FPGA外接EP子卡提供了接口。该子卡支持插入Gen5 X4、Gen4~1 X8的PCIe EP设备。此外RC8子卡还提供了Retimer芯片,有效的保证了Gen5高速信号的信号完整性。RC8子卡可以通过线缆从HS-PT100S设备的前面板直接取电,每根线缆提供30W的功率,并且RC8子卡上还预留了4Pin的ATX电源接口,可以实现外部供电。RC8子卡上有6个电源指示灯,指示灯全部常亮证明板卡供电正常。有4个业务面指示灯,D1常亮表示子卡初始化完成,D2闪烁表示子卡正常运行,D3表示当前链路的LINK速率(比如常灭-未建链、常亮-Gen5、4Hz-Gen4、2Hz-Gen3、1Hz-Gen2、0.5Hz-Gen1),D4为保留灯,默认常灭。

硬件连接:把PCIe 5.0的M.2固态硬盘安装在Gen5 RC子卡的金手指插槽内,再通过高速线缆将PCIe Gen5 RC子卡与PT100S连接。

子卡上建链状态指示灯被点亮,灯显示,RC子卡表的LINK_STATUS灯在不同PCIe速率等级下,建链后行为有差异:GEN5常亮,GEN4 4HZ闪烁,GEN3 2hz 闪烁,GEN2 1hz 闪烁,GEN1 0.5hz闪烁。

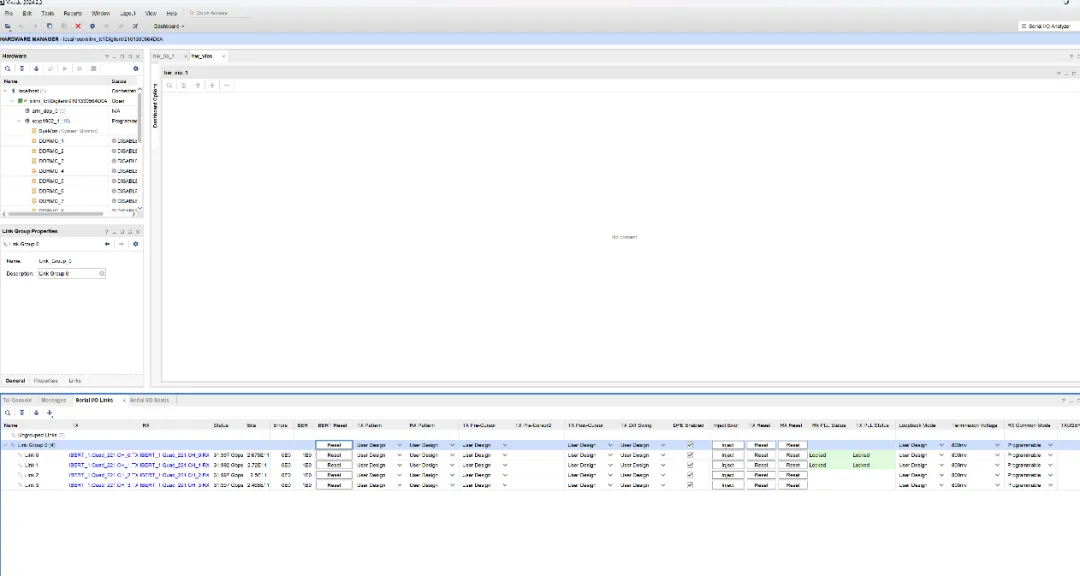

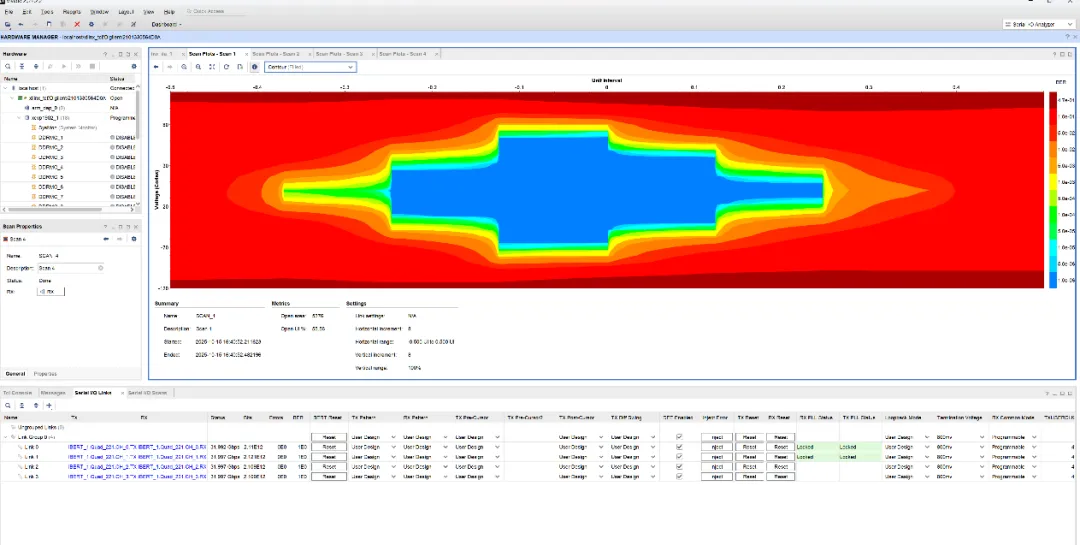

使用Vivado查看PCIe物理通道质量满足速率要求。

VeriTiger-PT100S原型验证平台不仅帮助实现PCIe Gen5,更为客户提供了一条通往Gen5应用的可靠捷径。它通过交付一个稳定、高性能且易于开发的硬件基础,让工程师能够将精力集中于利用Gen5的巨大带宽去创造下一代数据中心、AI和网络创新产品,而非纠缠于高频硬件设计的复杂性之中。

VeriTiger-PT100S正不断为更多前沿用户提供高效可靠的全场景验证解决方案,欢迎小伙伴们联系亚科鸿禹团队,获取更多前沿应用方案、深入技术交流: hypersilicon@hypersilicon.com 。