本工程实现PCIE的8通道速率2.2GBps通信,并验证数据的正确性。

本工程里已经把PCIE部分做成一个封装的模块,对外提供的是fifo_wr(数据发送fifo)接口和fufi_rd(数据接收的fifo接口),用户只要操作fifo接口,无需关心PCIE的内部驱动。为了便于读者更加明白,可以深入了解PCIE,我们将会制作一个PCIE的连载系列。

今天,首先说一下自定义AXI4的IP核,至于AXI4和PCIE之间有什么联系,敬请关注我们的连载系列文章。

在本篇文章中暂时先不讲解AXI4协议,先来分享例化AXI4的自定义IP核详细步骤。

一、 新建工程

为了节省篇幅,新建工程部分就不详细讲解,以下为我们新建好的工程:

二、 创建自定义IP

点击"Tools"菜单下的"Create and Package New IP",如下图所示:

按照指引,点击"next":

选择AXI4的IP核:

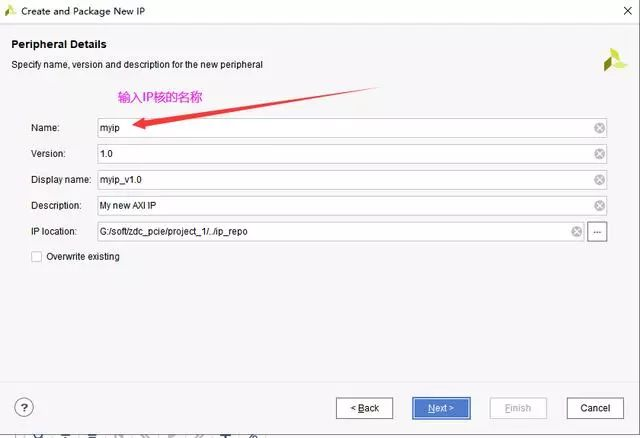

输入IP核的名称:

点击"next":

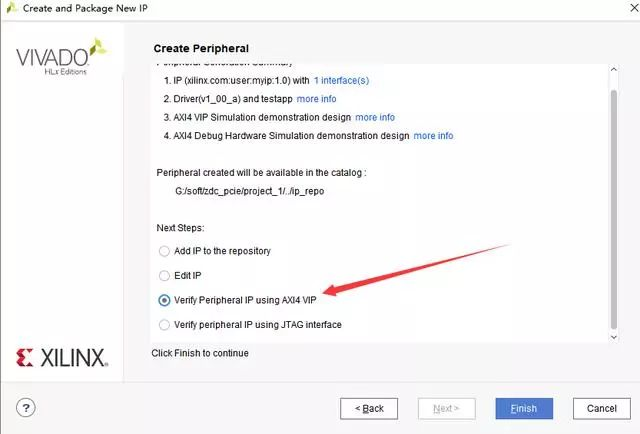

创建和使用AXI4的IP核

三、 生成BD文件

创建AXI4完毕之后系统会自动生成一个bd文件,如下图所示:

四、 修改IP

五、 修改需求

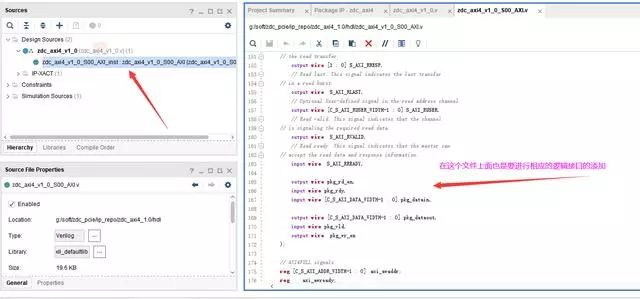

在修改IP核之后系统会自定的给我们打开另一个工程,我修改为我们自己的需求,打开的工程如下所示:

修改自己的逻辑,添加自己的逻辑端口:

六、 封装IP

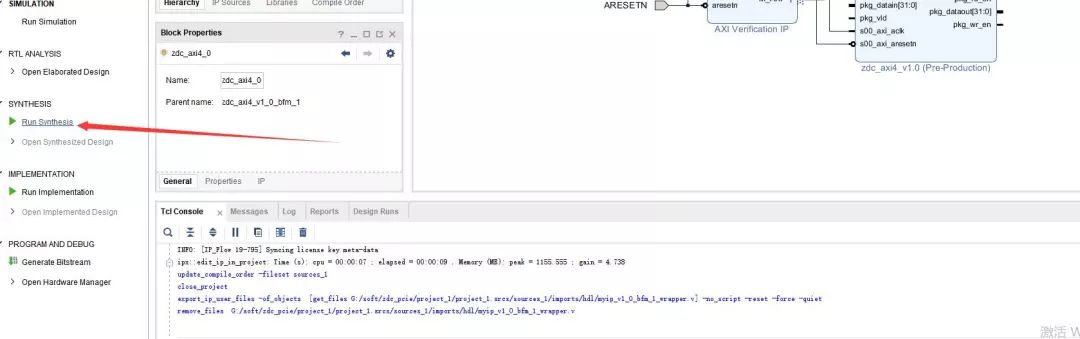

七、 验证IP

在bd文件空白的地方右键验证IP:

八、 编译程

九、 调用自定义IP

以上就是我们自行定义IP和调用IP的全过。