Vivado增量编译:加速FPGA设计实现的利器

judy 在 周二, 09/12/2023 - 10:25 提交

本文将介绍Vivado增量编译的基本概念、优点、使用方法以及注意事项

本文将介绍Vivado增量编译的基本概念、优点、使用方法以及注意事项

据Yole报道,处理器市场在 2021 年迎来了破纪录的一年,飙升至1555亿美元

查看MIG IP输出的init_calib_complete信号

AMD 将“牺牲台积电下一代Radeon游戏 GPU (RX 8000) 的产量,以提高 FPGA 和 GPGPU 的产量”

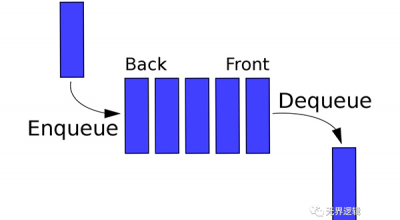

FIFO:First in, first out,先进先出;其主要作用是:数据缓存

内置校准: DDR3和DDR4控制器通常具有内置的校准机制

本文主要是记录MAC在RGMII接口中的设计。

本文将继续介绍最新版本 PDM 2023.1 的新增功能

Vivado综合工具支持多种属性设置,可以在RTL文件或XDC文件中进行设

本文将介绍如何在FPGA上快速搭建以太网