AMD剧透Siena处理器规格,最高64核128线程,瞄准电信和边缘计算市场

judy 在 周四, 08/31/2023 - 09:46 提交

面向电信和边缘应用场景的Siena处理器的关键规格

面向电信和边缘应用场景的Siena处理器的关键规格

本文分享BRAM资源使用优化策略

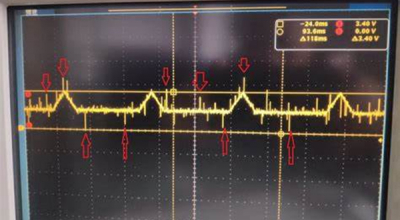

本文仅介绍几种常见的基于滤波器的方法的2D去噪

AMD发表年度企业责任报告,详述各项目目标进度

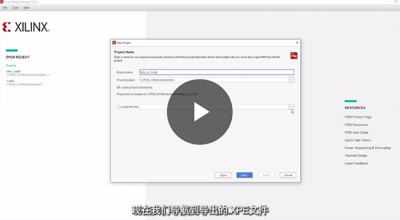

了解 Versal 器件功耗估计从 XPE 迁移到 PDM 的简易迁移路径

可编程逻辑系统通常部署在可能存在噪声的应用中

AMD MPSoC Linux一般使用PetaLinux编译Linux系统,包括Linux内核、DTS、文件系统

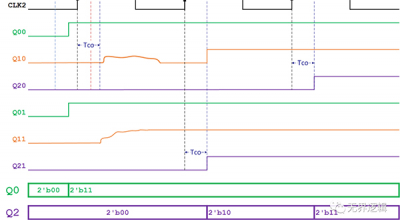

多bit信号跨时钟域如何处理呢?为什么不能使用两级打拍的方式呢?

本文介绍几种在FPGA中实用的PCIe接口应用方法

AMD下一代处理器肯定是Zen 5架构,尽管不确定会不会用3nm的制程