YunSDR通信小课堂(第27讲)

judy 在 周四, 03/13/2025 - 16:30 提交

本示例使用图8.7的模拟正交混频器接收器来接收以27GHz为中心的感兴趣信号,带宽为3GHz,如图8.8(a)所示

本示例使用图8.7的模拟正交混频器接收器来接收以27GHz为中心的感兴趣信号,带宽为3GHz,如图8.8(a)所示

基于AMD Zynq UltraScale+™ RFSoC Gen3 XCZU49DR 芯片的 16 通道 14 位 2.5GSPS ADC 与 16 通道 14 位 9.85GSPS DAC,实现全数字域直接射频采样

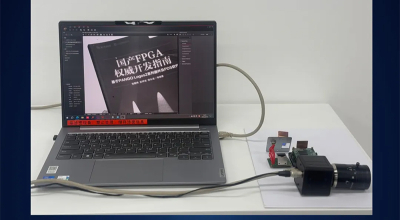

该方案基于Pango Logos系列PGL50器件、海图微CMOS Sensor HT501A和深目微GigE Vision IP方案共同实现

高性能“Zen 5”架构可提供服务器级性能与效率,并结合专属打造的功能,以优化产品寿命和系统弹性

下午有个朋友问我,现在AI发展这么快,怎么没听过FPGA有什么动静,难道FPGA就真的搭不上AI这趟列车了吗?

本文将介绍CXL 3.1标准的最新更新内容,包括新增的安全特性,以及如何持续为下一代基础结构提供内存池功能。

富士通采用 AMD Zynq RFSoC 数字前端( DFE )器件来提供具有成本效益、高容量和高能效的无线电,以满足不同市场需求

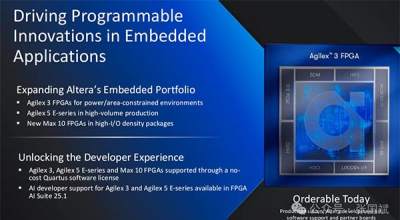

今天,随着Altera CEO Sandra Rivera宣布一系列重磅新品与技术进展,标志着这家独立运营的FPGA巨头正式迈入“Altera 2.0”时代

今天熊猫君分享一个基于AMD AU15P FPGA的SLVS-EC桥PCIe设计方案。

在 2025 国际嵌入式展上,Altera 发布了专为嵌入式开发者打造的最新可编程解决方案,以进一步突破智能边缘领域的创新边界