FPGA ISP Xilinx MIPI

judy 在 周四, 06/23/2022 - 09:34 提交

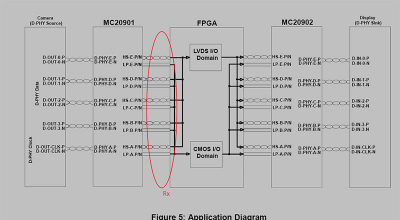

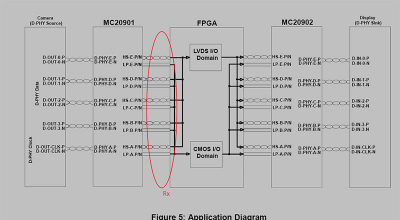

本人比较喜欢Xilinx家的东西,这里就讲一讲Xilinx家的MIPI方案。这里以普通7系列作为讨论的对象, X家高端的KU+/MPSOC+有已经可以直接支持MIPI接口的IO了。

本人比较喜欢Xilinx家的东西,这里就讲一讲Xilinx家的MIPI方案。这里以普通7系列作为讨论的对象, X家高端的KU+/MPSOC+有已经可以直接支持MIPI接口的IO了。

Xilinx 用于程序固化的MCS文件虽然是以.mcs后缀命名,但其本质是hex文件,把后缀改成.hex后,可以直接使用文件工具打开,符合Intel-HEX文件格式。

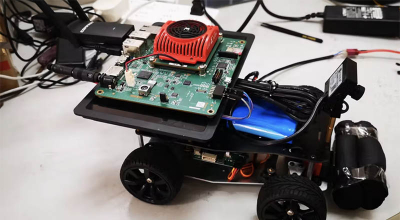

在ROS机器人框架下设计了一套基于视觉信息和神经网络的小车自动驾驶程序,并部署在KV260平台上。

RAM是Random Access Memory的首字母缩写。它是一种主存储器,用于存储当前正在使用的信息。信息可以是正在处理的数据或程序代码。

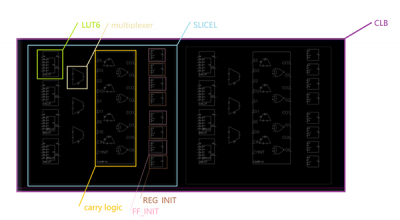

之前很多人问我有没有好的代码可以参考,我之前一直推荐的是官方的IP参考例程/IP源码,但是不知道大家有没有看过官方的项目例程,看下下图

LVDS是一种低摆幅的差分信号技术,使得信号能在差分PCB线对或平衡电缆上以几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

Zynq UltraScale+ MPSoC EV系列含有大量的视频输入接口,接入的视频流经过PL侧的逻辑处理后,通过USB3.0实现UVC输出各种高分辨率、高帧率、特殊格式的视频流

本文提供优化神经网络模型的能力。

移位寄存器内的数据可以在移位脉冲(时钟信号)的作用下依次左移或右移。移位寄存器不仅可以存储数据,还可以用来实现数据的串并转换、分频,构成序列码发生器、序列码检测器

做FPGA的人很多,但其中做原型验证的人可能就比较少了,我做了一年多的FPGA原型验证,今天简单聊聊自己的一点感触。