了解ADX4 IP可在任何输入频率和温度下提高ADC的射频性能

judy 在 周四, 06/30/2022 - 09:04 提交

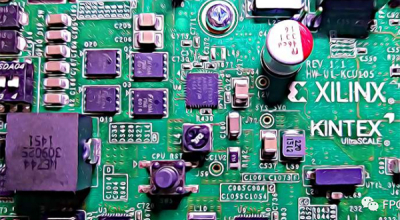

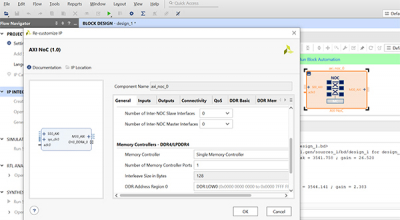

本视频教程阐述了如何创建一个Vivado工程,以及如何基于VHDL设计案例和EV12AQ600-ADX-EVM演示板,在Kintex Ultrascale FPGA上实现ADX4 IP。

本视频教程阐述了如何创建一个Vivado工程,以及如何基于VHDL设计案例和EV12AQ600-ADX-EVM演示板,在Kintex Ultrascale FPGA上实现ADX4 IP。

Versal AI Core 系列具备的高性能和超低时延处理能力显著缩短了图像处理时间,与传统架构的几分钟时间相比,这种架构能够近乎实时地生成直播回放

本文旨在帮大家了解如何在运行 Ubuntu 桌面的 Xilinx KV260 Vision AI 入门套件上轻松设置机器学习推理功能。

之前很早就听说了FSMC接口用于MCU与FPGA之间的通讯。最近使用的一款MCU与FPGA之间通讯,FPGA模拟成NAND Flash作为Memory让MCU读写

我们将介绍使用 Vivado 硬件管理器对开发板闪存进行编程的步骤。

本文描述为 Xilinx® 器件设计散热器和散热解决方案的指南和最佳实践。

今天我们来介绍一下I/O planning方面的设计考虑和实现流程。

该项目将借助 KV260 上的 PYNQ -DPU 覆盖,从而能够使我们在 LiDAR 点云上进行 3D 对象检测比以往任何时候都更加高效!

CLB实际上是四种基本元素的集合----查找表LUT,进位链CARRY4,多路选择器Multiplexer以及存储单元FF。

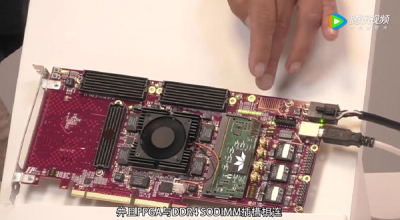

观看这个短视频,了解如何连接Teledyne e2v耐辐射DDR4存储器与AMD XILINX Kintex Ultrascale FPGA KU115。