免触摸界面和数据分析

judy 在 周一, 02/14/2022 - 09:55 提交

这种眼动追踪辅助技术可用你的眼睛创建一个交流工具来增强运动控制。通过校准眼球运动,该技术使用人工智能来跟踪角膜反射和瞳孔定位。 通过交互式演示,您可以进行校准,然后玩各种展示眼动追踪技术的游戏。

这种眼动追踪辅助技术可用你的眼睛创建一个交流工具来增强运动控制。通过校准眼球运动,该技术使用人工智能来跟踪角膜反射和瞳孔定位。 通过交互式演示,您可以进行校准,然后玩各种展示眼动追踪技术的游戏。

在Vivado中,可能由于某些逻辑输入悬空而导致Implementation的opt_design时会错

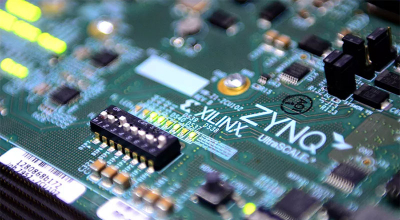

本文描述了Xilinx®针对Open RAN无线电的解决方案。

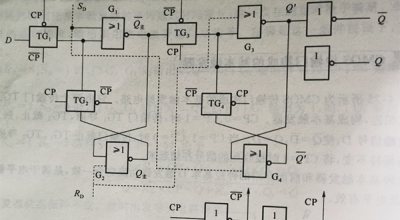

同步电路系统设计将系统状态的变化与时钟信号同步,并通过这种理想化的方式降低电路设计难度。同步电路设计是FPGA设计的基础。但是伴随着集成电路的微缩化和大规模化,同步式电路的一些问题也显现出来。

让我们一起看一下全国大学生FPGA创新设计竞赛(FPGA创新赛)和中国研究生电子设计竞赛(研电赛)这两大赛事中的三个优秀作品

使用 Vivado 2021.1 或更高版本实现的所有 Versal 集成内存控制器接口都支持 2D 眼图扫描功能。2D Eye Scan 可用于检查每个字节通道的健康状况,并允许图形比较以快速识别布局和开发板相关问题。

我们常说一句话:工欲善其事,必先利其器。作为一名FPGA工程师,我们的任务就是把某些特定的逻辑行为雕刻到FPGA芯片上,通过设计逻辑电路达到预期目的。

以前为ARM64编译软件包,直接在Makefile里指定交叉编译器、sysroot的路径,就能成功编译。

在 2021 OCP 大会上,Xilinx 网络与计算存储产品部负责人 Kartik Srinivasan 做了报告。该报告概括介绍 Xilinx 如何将异构加速引擎结合起来,为满足数据中心网络的动态需求提供最高效方法。

在 Zynq UltraScale+ MPSoC/RFSoC 器件中,Linux CPU Idle 默认启用。启用后,Linux 会在 CPU 内核空闲时关闭它们(与 WFI 相对)。当连接xsdb时,这可能会导致问题。