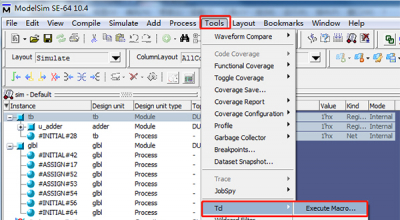

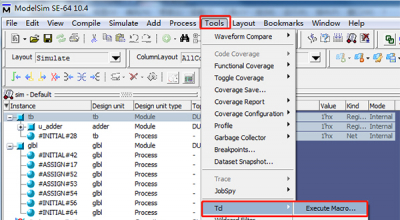

老鸟的姿势学起来,用脚本进行modelsim仿真

judy 在 周四, 02/17/2022 - 09:50 提交

老鸟的姿势学起来,用脚本进行modelsim仿真

老鸟的姿势学起来,用脚本进行modelsim仿真

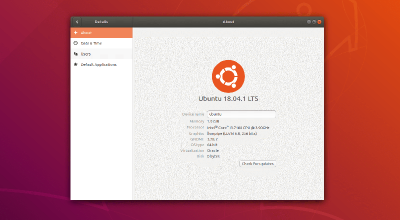

所有工具和参考设计使用2021.2。X86编译主机的操作系统是Ubuntu 18.04.6 LTS。

先从运行一个创建一个项目开始吧。

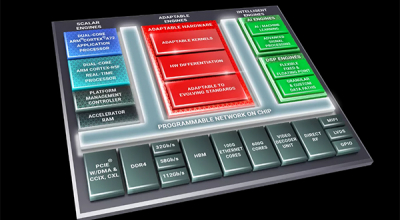

赛灵思 Versal® 套件计算加速平台 (ACAP) 设计方法论是帮助 Versal 设计流程的一整套计算实践。这必须让用户进行这些设计的操作下载能力和复杂性,因此通过特定的步骤设计任务确保设计完成并成功完成。

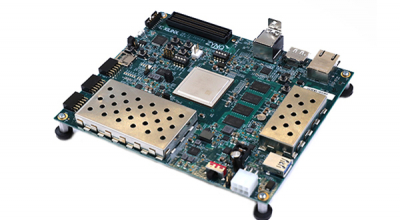

ZCU104 开发板基于Xilinx 公司Zynq UltraScale +XCZU7EV-2FFVC1156 MPSoC器件设计,支持嵌入式视觉使用案例的许多常见外设及接口

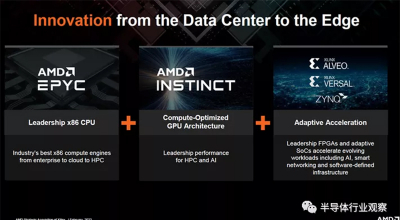

过去几年里,计算行业见证了数据的大规模爆发以及机器学习( ML )与 AI 应用的激增。其结果是对更高吞吐量和实时计算能力愈发强烈的需求,与此同时还要保持灵活应变能力,以便跟上不断演进的工作负载需求和不断变化的协议。

AMD 周一宣布完成了对 Xilinx 的收购,创建了一家可以提供各种类型计算设备的公司,当中包括 CPU、GPU 和 FPGA。此举将帮助 AMD 继续扩大其在数据中心领域的影响力

在Ubuntu 18.04下使用Vivado Jtag加载FPGA,发现找不到器件。

AMD今天宣布以全股份交易(all-stock transaction)方式完成对赛灵思(Xilinx)的收购。

在解答相关问题的时候有碰到过cl_invalid_work_group_size的错误,然后通过报错信息在XRT