如何 在 UltraScale+ 设计中使用 CPLLPD 引脚

judy 在 周二, 10/19/2021 - 09:57 提交

在 UltraScale+ 收发器中,CPLL 用于设计时,有一个校准块必须使用,才能确保 CPLL 的功能正确。该模块使用 CPLLPD 引脚,因此不能用于其正常功能。

在 UltraScale+ 收发器中,CPLL 用于设计时,有一个校准块必须使用,才能确保 CPLL 的功能正确。该模块使用 CPLLPD 引脚,因此不能用于其正常功能。

学习如何在 Vitis 环境中使用 Ultra96-V2 开发板进行开发。

FPGA中跨异步时钟处理的方法,是面试中经常碰到的问题,也是我们平时工作中经常会碰到的场景,对于单bit的跨异步时钟处理,我们最常用的方法就是打两拍,但这时这两级寄存器最好是放到同一个Slice中,比如下面的代码

公众号文章《业界第一个真正意义上开源100 Gbps NIC Corundum介绍》和《揭秘:普通电脑换上Xilinx Alveo U50 100G网卡传文件会有多快?》发出后,得到了很多粉丝的关注,大家纷纷留言询问重现开源工程的详细过程。团队李钊同学详细写了一下具体的实现步骤,具体如下

如果给 DCM/PLL/MMCM 的输入时钟施加 PERIOD 约束,约束会自动传递给输出时钟。这些时钟被视为相关时钟而跨时钟域路径由时序分析器进行分析,我该如何从时序分析中排除跨时钟域路径呢?

本文转载自:亦梦云烟的博客

简介

PetaLinux是一个嵌入式Linux系统开发工具,用于设计Xilinx基于FPGA的SOC片上系统。本节为第一节,旨在介绍如何使用PetaLinux工具。

软件环境: windows 10 64bit,VMware 12, ubuntu 16, Vivado2018.2

硬件环境: 米尔科技Zturn board

安装vmware后在其中安装ubuntu。

一、安装PetaLinux开发环境

安装PetaLinux要求:

在非root权限下安装

PetaLinux依赖很多标准开发工具和库,需要先安装下表中的依赖。

表1-1 Packages and Linux workstation Environments

生产线已步入了快节奏时代, 但要提高交付速度和客户满意度,势必需要在装运前检测制造或包装缺陷。然而,自动化检测设备需要在不降低生产线速度的情况下进行处理和做出决策。所以,我们需要借助于Xilinx Kria K26系统模块 (SoM)等器件的帮助。接下来让我们将详细地介绍Kria KV260视觉入门套件如何用于制造行业。

本文描述 Xilinx® Runtime (XRT) 的发布。

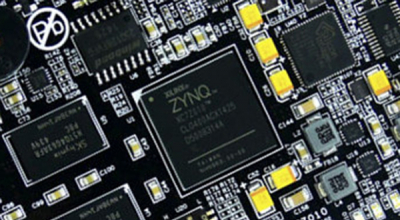

板子使用的是米联客的XC7A35TFGG484-2的开发板,上面带有256MB的型号为Micron MT41K128M16的DDR3内存。板子上的V4引脚上接了50MHz的晶振。

用MIG核来驱动这片DDR3内存。DDR3的运行时钟Clock Period为400MHz(由MIG核自己产生这个时钟,从ddr3_ck_p和ddr3_ck_n引脚输出出来,用来驱动DDR3)

我们如何通过 XDC 使用数据初始化 Block RAM?