在高速网卡中实现可编程传输协议

judy 在 周五, 10/08/2021 - 15:42 提交

本文通过设计Tonic(一种用于传输逻辑的灵活硬件架构)来实现高速网卡中的可编程传输协议。在100Gbps的速率下,传输协议必须每隔几纳秒在NIC上仅使用每个流状态的几千比特生成一个数据段。通过识别跨不同传输协议的传输逻辑的通用模式,我们为传输逻辑设计了一个高效的硬件“模板”,该模板在使用简单的API编程的同时可以满足这些约束。

本文通过设计Tonic(一种用于传输逻辑的灵活硬件架构)来实现高速网卡中的可编程传输协议。在100Gbps的速率下,传输协议必须每隔几纳秒在NIC上仅使用每个流状态的几千比特生成一个数据段。通过识别跨不同传输协议的传输逻辑的通用模式,我们为传输逻辑设计了一个高效的硬件“模板”,该模板在使用简单的API编程的同时可以满足这些约束。

AnDAPT采用集成、灵活和可编程AmP电源管理IC来支持为Xilinx Kintex和Artix FPGA以及子系列产品设备供电。

本文整理自Xilinx公开课:Vivado时序收敛技术。有些知识在公开课中讲的并不是很细,因此我又对齐进行了整理,分为了几篇文章。

BitGen 的输出文件有什么用处,什么时候会生成这些文件?

赛灵思今日宣布,其现场可编程门阵列( FPGA )和自适应片上系统( SoC )器件正为一系列索尼电子产品提供支持,用于专业音视频( A/V )应用,包括最新 XVS-G1 4K 直播制作切换台。赛灵思与索尼强强联手,借助双方前沿技术共同打造世界上最先进的音视频产品,用于拍摄和转播全球现场活动。

如今各种机器学习框架的普及使得个人搭建和训练一个机器学习模型越来越容易。然而现实中大量的机器学习模型训练完后需要在边缘端部署,那么我们看看借助Xilinx Vitis-AI工具,如何仅仅使用10行代码,就能在ZYNQ MP器件上部署深度学习模型实现图像分类。

有些产品中,使用VCU解码图像后,还需要做一些特殊的处理。如果直接把地址传递给特殊处理模块,大多数情况运行正常,有时会发现数据错误。这个问题,是因为显示函数释放buffer造成的。解码前,解码器从buffer管理模块申请buffer。

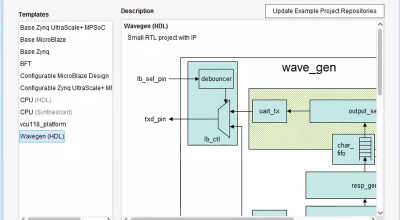

本篇文章我们以Vivado的wave_gen工程为例,来看下如何通过ECO来增加一个LUT,并对内部信号实现取反的功能。

XILIINX开发者社区于09.22携手电巢直播平台进行了硬件平台+开发技巧+赛制详解的直播详解活动,为了便于更多的小伙伴学习,我们整理了本次直播的回放,帮助更多的的开发者和本次参赛者更好的理解赛灵思的AI技术路线,为您的参赛项目提供一些借鉴和参考。

FPGA是电子器件中的万能芯片,Xilinx FPGA处于行业龙头地位更是非常灵活。FPGA管脚兼容性强,能跟绝大部分电子元器件直接对接。Xilinx SelectIO支持电平标准多,除MIPI C-PHY电平(三电平标准)外,IO能直接对接3.3V以及3.3V以下基本所有电平标准,初步统计支持72种不同电平标准。