Vivado IP中的Shared Logic到底是干嘛的?

judy 在 周五, 09/17/2021 - 15:29 提交

在很多Vivado的高速接口的IP中,比如Ethernet、PCIe、SRIO的设置中,都会有个Shared Logic的页面。可能很多同学并没有很关注这个页面,直接默认设置就完事了。但其实这个页面的内容也是非常有用的,我们可以看到页面中有两个选择:

在很多Vivado的高速接口的IP中,比如Ethernet、PCIe、SRIO的设置中,都会有个Shared Logic的页面。可能很多同学并没有很关注这个页面,直接默认设置就完事了。但其实这个页面的内容也是非常有用的,我们可以看到页面中有两个选择:

不同设计里,Linux DRM子系统里设备ID不一样。每次修改,费时费力,也容易出错。因此写了以下脚本,自动查找encoder_id,crtc_id,connector_id等。然后在后续命令和脚本中,可以直接引用。

目前,业界已经有多种成熟的计算平台,比如CPU、GPU、DSP等,为什么还需要自适应计算这种新的计算形式呢?对于这个话题,赛灵思人工智能及软件市场总监罗霖(Andy Luo)先生给出了以下几点原因。

在虚拟机中的ubuntu中开发linux系统驱动程序,往往直接使用gedit编辑,makefile编译,而这种方法比较麻烦;Eclipse是开源软件框架,编辑器比较好用,配置好编译器后可以更加方便快捷的开发程序,本文介绍如何使用Eclipse开发Linux的驱动程序。

本视频展示了如何使用智能模型选型示例开始使用 VVAS。

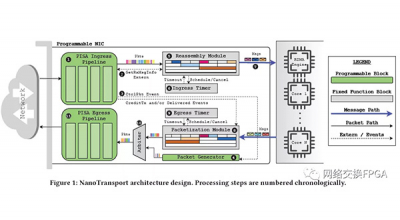

本文继续推荐Nick教授团队在相同的开源工程nanoPU的基础上做的进一步工作,将传输层进行硬件化的定制加速,可以在不到10ns的时间内处理传输层中的数据包,并且可以每2.6ns发出一个新数据包。

Vitis AI提供两种应用例程,VART和Vitis AI Library,下文详细描述了VART中自动驾驶应用的实现过程。

继2020年首届赛灵思自适应挑战赛完美收官后,近期Xilinx携手Hackster.io再次发起挑战!考验开发者将赛灵思自适应计算平台与Vivado设计套件、Vitis开发环境和Vitis AI相结合的能力,一切为解决实际问题而来!

本篇博客将为您演示如何使用此报告来帮助加速调试,甚至完全避免硬件故障,最后确定此问题根本原因是校准完成时出现争用状况。出现争用状况的原因是由于某个多周期约束所覆盖的时序例外,由此导致在时序分析报告中并未标记此问题。

本文为解决基于C++的传统定价程序带来的处理时间长、延迟高、处理速率低的问题,提出并实现了一种基于FPGA的并行流水线计算处理设计,能够完成对雪球期权的定价功能,并使用HLS开发模式对设计进行了实现。