Xilinx Adapt 2021 拉开帷幕,面向软硬件开发者展示全新解决方案与技术

judy 在 周三, 09/08/2021 - 10:00 提交

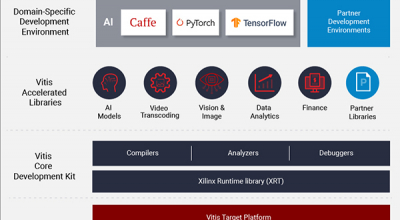

赛灵思今日于公司虚拟技术大会 Xilinx Adapt 2021 首周宣布,推出功能强大的全新解决方案和 IP,旨在满足其快速壮大的软件、AI 和硬件开发者社区需求。2021 年 11月 16 日,Xilinx Adapt 2021 China 虚拟活动也即将上线。Adapt 2021 China 作为中国专场内容,将面向中国市场、由赛灵思本地发言人、合作伙伴与客户带来众多精彩内容。