Vivado的Implementation都包含哪些步骤?

judy 在 周三, 09/15/2021 - 11:32 提交

Vivado的Implementation主要有三大步:

opt_design,会生成opt_desgin.dcp

place_design,会生成place_design.dcp

route_design,会生成route_design.dcp

Vivado的Implementation主要有三大步:

opt_design,会生成opt_desgin.dcp

place_design,会生成place_design.dcp

route_design,会生成route_design.dcp

自适应计算加速平台(ACAP)是一个完全软件编程的异构计算平台,它结合了标量引擎、自适应引擎、智能AI和DSP引擎,可极大地增加数据中心、无线网络、汽车驾驶辅助和有线通信应用的计算能力。

UBIFS是更强壮的FLash文件系统。很多嵌入式系统都使用了UBIFS。Xilinx PetaLinux 2018.2也支持UBIFS。只需要在Linux/U-Boot里添加相关配置选项,就能为QSPI Flash创建UBIFS。

Vitis AI提供两种应用例程,VART和Vitis AI Library,下文详细描述了Vitis AI Library中refinedet应用的实现过程。

本文记录了Vivado®使用设计运行策略和单个实现命令进行放置和路由的实现功能。详细介绍了用于快速修改现有设计的增量编译流程,以及对信号路由路径进行精确控制的手动路由方法。

VVAS 是一个完整的软件堆栈,用于在所有 Xilinx 平台上构建基于 AI 的智能视频分析解决方案!在短短几周内实现从概念到实时部署。

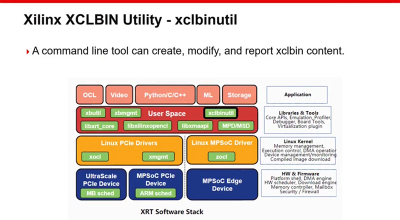

Xilinx 提供了一个基于命令行的自包含实用程序,称为 xclbinutil。 您可以将其用于 Xilinx 加速器二进制容器文件(.XCLBIN)。本视频将带您了解使用 xbutil 检查、报告并修改 xclbin 内容的基本步骤。

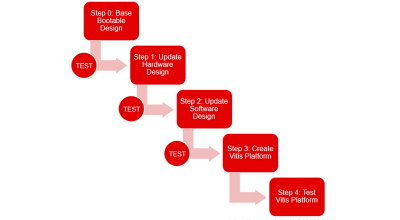

Xilinx提供了一些基础的开发板平台内嵌在Vitis IDE中,用户可以直接从这些platform创建应用程序。但如果是自定义的板卡或者想要部署更多加速器IP、配置不同的性能,我们就需要创建完全自定义的硬件平台。本文介绍创建Vitis AI硬件平台的基本步骤。

将zynqmp单板和电脑主机通过网线连接到同一个交换机。单板和电脑上电后,打开虚拟机,将网络连接设置成桥接模式。进入虚拟机,查询虚拟机ip地址

I/O 信号可通过 MIO 引脚获得, Quad-SPI 控制器在共享或单独的总线配置中最多支持两个 SPI 闪存, 控制器支持以多种配置运行