2021 FPGA创新赛线上Xilinx专题技术培训

judy 在 周五, 09/10/2021 - 15:29 提交

本次系列培训将面向2021年FPGA创新赛师生参赛团队与广大Xilinx FPGA用户。藉此培训让大家了解基于Xilinx FPGA设计流程,包括基础逻辑设计与调试、嵌入式系统设计、PYNQ框架介绍与DPU的使用等。涵盖范围将适配逻辑设计、嵌入式设计、数据科学设计的不同应用需求。

本次系列培训将面向2021年FPGA创新赛师生参赛团队与广大Xilinx FPGA用户。藉此培训让大家了解基于Xilinx FPGA设计流程,包括基础逻辑设计与调试、嵌入式系统设计、PYNQ框架介绍与DPU的使用等。涵盖范围将适配逻辑设计、嵌入式设计、数据科学设计的不同应用需求。

本篇博文中的分析是根据真实客户问题撰写的,该客户发现在现场出现罕见的比特翻转, 本篇博文旨在演示用于缩小根本原因范围以及修复此问题的部分调试技巧。

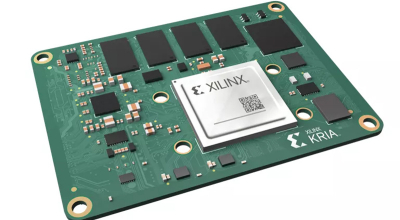

产品是企业意志的直接体现,Xilinx先后推出可为FPGA、SoC 和 Versal ACAP开发嵌入式软件和加速应用的Vitis统一开发平台,面向AI时代的Alveo加速器、Kria机器人自适应解决方案,已为包括微软Azure Synapse在内的诸多项目提供创新支持,Xilinx深深影响着数据中心、医疗、机器人等产业。

经过前面的实验,我们已经基本摸清楚了Vitis IDE & Vivado的使用方法。在开始构建DPU与深度学习软件栈之前,我们先对我们拿到的开发板做个体检(硬件全面测试),由于大部分深度学习软件框架都是运行在Linux, android或IOS等嵌入式系统上,因此测试完硬件后还需要搭建一个Linux系统以供后续开发使用。

体现 Versal 器件价值主张的参考设计。平台设计包括针对不同市场的视频、机器学习和基于 100G 以太网的 IP。用户可以按原样使用这些设计,也可以根据应用需求对其进行修改。

对一个全新的加速应用程序有激动人心的想法吗? 在2021年赛灵思自适应计算挑战中展示它吧!

Ubuntu中安装python虚拟环境

在博客文章 使用 AXI performance monitors (APM)测试MPSoC DDR访问带宽 中介绍了DDR带宽测试工具"apm_main.elf"。使用过程中,发现还有些不足。它只能测试端口1/2/4/5,只能打印带宽。很多场合需要更多信息。于是更新了这个工具,可以测试所有端口

Versal™ 自适应计算加速平台 (ACAP) 将标量引擎 (Scalar Engine)、自适应引擎 (Adaptable Engine) 和智能引擎(Intelligent Engine) 与领先的存储器和交互技术有机结合,从而为任何应用提供强大的异构加速功能。Versal 架构 PCB 准则已基于前几代进行了精简,以方便 PCB 布局专业人员和硬件设计师使用。

以前设计一个产品时,先要规划好硬件架构,等硬件设计全部完成后,才会开始软件部分的开发,然后才是完整产品的发布。现在,随着云计算、互联网的发展,以及AI、5G和自动驾驶的兴起,硬件和产品的开发流程需求在发生着前所未有的变化,比如更高的硬件性能、更高的安全和保密需求、不断增加的传感器类型和接口、不断演进的AI算法和模型,以及软件开发需要与硬件开发同步进行等等