【工程师分享】 解决PetaLinux工程FSBL do_configureh错误

judy 在 周二, 11/24/2020 - 14:18 提交

更换PetaLinux工程的HDF/XSA文件后,PetaLinux工程编译出现FSBL do_configureh错误。使用命令“petalinux-build -x mrproper -f ”,彻底清除工程,再编译工程,不再有问题。

更换PetaLinux工程的HDF/XSA文件后,PetaLinux工程编译出现FSBL do_configureh错误。使用命令“petalinux-build -x mrproper -f ”,彻底清除工程,再编译工程,不再有问题。

由于网络配置的复杂性,大多数安全和网络监视设备都会收到大量重复数据包。部署在 Alveo 加速卡上的 Accolade FPGA IP 将在所有重复的数据包到达主机应用程序之前快速有效地消除它们。利用此功能,可以回收大量浪费的 CPU 周期并将其用于更高价值的处理。

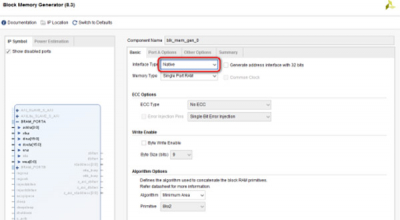

Vivado2017.2 中BRAM版本为 Block Memory Generator Specific Features 8.3。BRAM IP核包括有5种类型:Single-port RAM 单端口RAM,Simple Dual-port RAM 简单双端口RAM(A写数据B读数据)

冬天快要到了,细菌们到了卷土重来的季节,那么为了针对细菌的抗生素耐药性,我们该怎么快速地发现对应的药物呢?来自思克莱德大学的Ryan Greer在OpenHW2020中,利用了PYNQ上的支持向量机,通过使用分类算法,从来自抗生素生产菌的高光谱图像中快速识别细菌菌株的特性。

有的时候需要查找一些官网的例程进行学习和参考,但是总感觉无从下手,今天就教大家怎么利用官网和Vivado的Documention进行相关的操作。

使用Xilinx VCU TRD 2020.1 Audio工程测试1080p yuv422 10bit编码,软件报告VCU能力不足,错误信息是“Codec error: Channel creation failed, processing power of the available cores insufficient”。

当您多次执行 RPU 的挂起/恢复时,它只在挂起/恢复的第一个周期起作用。在挂起/恢复的第二个周期,RPU 在第一次 IPI 调用时挂起。

在本篇博文中,我们将探讨如何在 Vitis™ 中使用 UIO 驱动框架创建简单的 Linux 用户应用。

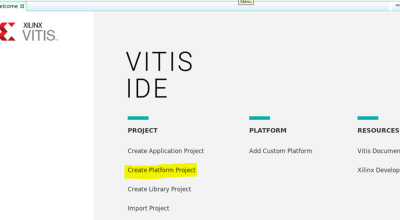

赛灵思公司(Xilinx)推出Vitis——这是一款统一软件平台,可以让包括软件工程师和AI科学家在内的广大开发者都能受益于硬件灵活应变的优势。历经5年、投入总计1000人打造而成,Vitis统一软件平台无需用户深入掌握硬件专业知识,即可根据软件或算法代码自动适配和使用赛灵思硬件架构。

Ryamax®Smart NIC 支持的云加速解决方案旨在满足 Web 级云和网络需求。通过利用“开放标准、平台和软件定义“的方法,我们提供了从软件到硬件的白盒 Smart NIC 解决方案,以减轻 CPU 负荷并响应实时数据中心网络的服务请求。