如何在 ZCU104 上实现智能视频分析

judy 在 周五, 11/13/2020 - 09:35 提交

本节公开课我们通过一个实例演示带领大家学习如何在 ZCU104 评估套件上创建和运行视频分析的应用,该演示用到了 VCU(视频处理单元)、DPU(数据处理单元)以及对 PL(可编程逻辑)部分的编程和配置。

本节公开课我们通过一个实例演示带领大家学习如何在 ZCU104 评估套件上创建和运行视频分析的应用,该演示用到了 VCU(视频处理单元)、DPU(数据处理单元)以及对 PL(可编程逻辑)部分的编程和配置。

测试环境:Xilinx ZCU106 单板

Xilinx VCU TRD2020.1

Linux 内核配置:根据文档Docker on Zynq Ultrascale+ (Xilinx Yocto Flow),在PetaLinux工程的文件project-spec/meta-user/recipes-kernel/linux/linux-xlnx/user.cfg里添加下列配置项。

如果在 85 摄氏度以上的工作温度下运行,DRAM 需要更频繁地更新。对于 PS DDR4/DDR3,更新周期必须减半。如果不进行调整,可能会出现数据丢失/损坏的情况。

本白皮书介绍了如何运用基于赛灵思技术的先进成像方法实现更优异的成像画质、速度和准确性。平面波和合成孔径成像是本白皮书主要介绍的两种方法,它们为心壁运动、血流和心脏外科手术等难以管理的特定诊断和外科手术带来可观的帧率和准确性提升。

ZYNQ-7000系列MIO/EMIO/AXI_GPIO接口

赛灵思公司与三星电子有限公司今日宣布推出三星 SmartSSD® 计算存储驱动器(CSD)。基于赛灵思 FPGA 的 SmartSSD CSD 是业界首款灵活应变的计算存储平台,能够提供数据密集型应用所需的性能、定制能力和可扩展能力。

足不出户,即可了解5G行业最新趋势,以及赛灵思T1 Telco加速器卡、集成硬化IP的Zynq RFSoC DFE、Versal AI Core等5G最新产品与方案。

随着基于云的网络的增加,企业网络中的流量已经大大增加,数以百万计的流量流入和流出企业网络。下一代防火墙安全设备需要高吞吐量的高级安全威胁缓解策略和恶意软件检测功能。下一代防火墙正在从低吞吐量(1-10Gbps)的基于软件的流量检查设备进化为高吞吐量(100-400Gps)的状态流量检查设备,这些设备实现了基于流量的动态网络流量策略规则

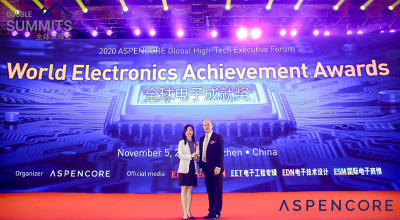

11 月 5 日,致力于加速人工智能推断的赛灵思开发软件平台——Vitis AI,在全球电子工程领域知名媒体机构 ASPENCORE 主办的“2020 全球电子成就奖(World Electronics Achievement Awards,WEAA)”评选活动中,荣膺“2020 全球电子成就奖年度软件/工具”。

在一个工程里,有两个Xilinx AXI DMA。其中一个AXI DMA设备是用于调试的。任何时候,其实只使用一个设备AXI DMA设备。软件使用了bperez77_xilinx_axidma的内核和用户态驱动。