关于ZCU104开发板VADJ__FMC电压无输出的回答

judy 在 周五, 10/30/2020 - 09:24 提交

最近有不少同学在使用ZCU104开发板时遇到板上电压VADJ__FMC无输出的情况,熊猫君在这里越俎代庖冒充FAE做一下回答:

最近有不少同学在使用ZCU104开发板时遇到板上电压VADJ__FMC无输出的情况,熊猫君在这里越俎代庖冒充FAE做一下回答:

在本文中,我们将以部署到 FPGA 的 IIR 滤波器为例,介绍本机浮点工作流。然后,我们将回顾使用定点的挑战,并比较使用单精度浮点或定点时面积和频率之间的取舍。我们还将展示浮点和定点的组合如何减少实际设计中的转换和实现时间,同时提供更高的精度。您将看到浮点如何在具有高动态范围要求的实际设计中显著缩小面积并提高速度

体验全新 Zynq® RFSoC DFE,一类具有突破性意义的自适应无线电平台,面向 5G 无线电大规模部署。全新自适应无线电平台融合了适应不断演进的 5G 标准的灵活性,以及旨在实现高性能、低功耗与高成本效益的硬化无线电数字前端。

在这个直播课程中,我们将为大家详细介绍 Vitis 加速库,讲解库的构成和分类,以及如何在 Vitis 开发环境及 Xilinx 硬件平台上分层应用最适合的 Vitis 加速库。我们还会以 Alveo U50 加速卡为例,选取 Vitis 加速库中的一个压缩算法 Zlib 为例,详细介绍算法的构成、性能,并实例展示如何在 U50 板卡上实现 Vitis Zlib 算法库。

第三届中国国际进口博览会即将拉开帷幕,致力于“打造灵活应变,万物智能世界”的赛灵思公司,将携手国内外部分合作伙伴,展示一系列先进的平台和解决方案,面向与我们的日常生活息息相关的智能驾驶、智慧工厂、智慧交通、智慧质检,以及智慧物流等智能世界,为开发者及创新者将创意变成现实助力,让我们的生活更加便捷、智慧。

如同4G一样,5G技术也是在建设和商用中不断完善,这会导致接入网设备设计挑战不断提升,如何应对这样的挑战?我们来看看擅长自我突破的赛灵思这回又捣鼓出了 什么新品?

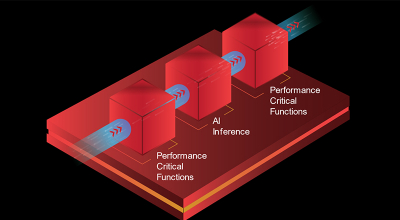

AI 已经开始改变我们生活的方方面面,推动了显著的社会进步。从自动驾驶汽车到 AI 辅助医疗诊断,我们正处于一个真正的变革时代的开端。但是,有机遇就会有挑战。AI 推断作为采用经训练的机器学习算法开展预测的过程,无论是部署在云端、边缘还是终端,都要求在严格的功耗预算下提供优异的处理性能。

据外媒报道,AMD表示,已经同意以350亿美元全股票交易收购赛灵思,这将加剧它与英特尔在数据中心芯片市场的竞争。AMD预计该交易将在2021年底完成,合并后的公司市值1300亿美元左右,将拥有13,000名工程师,采取全部外包的生产策略,主要依靠台积电进行生产。这两家美国公司已经从更加灵活的策略中获益,从受到内部生产困扰的英特尔手中抢夺市场份额。

Zynq RFSoC DFE 将硬化的数字前端(DFE)模块与灵活应变的可编程逻辑相结合,为涵盖低、中、高频段频谱的广泛用例打造了高性能、低功耗且经济高效的 5G NR 无线电解决方案。Zynq RFSoC DFE 在采用硬化模块的 ASIC 的成本效益与可编程与自适应 SoC 的灵活性、可扩展性及上市时间优势之间,实现了绝佳技术平衡。

这是《创建 Vitis 加速平台》系列的第 3 篇博文。在前文中,我们讲解了如何创建硬件和软件工程。在本文中,我们将讲解如何在 Vitis™ 中将所有这些工程封装在一起。