PCIe系列第七讲、PCIe的物理层

judy 在 周二, 07/28/2020 - 09:39 提交

本章将着重讲述PCIe物理层组成与操作,物理层位于数据链路层之下,可产生PLP包(Physical Layer Packet)进行管理。

本章将着重讲述PCIe物理层组成与操作,物理层位于数据链路层之下,可产生PLP包(Physical Layer Packet)进行管理。

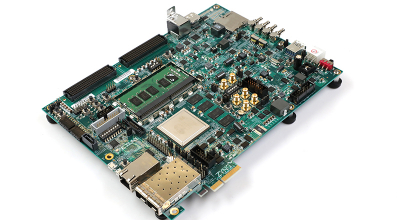

250-M2D 采用了完全可编程的赛灵思® Kintex® UltraScale+™ FPGA,直接耦合到本地 DDR4 内存的两个存储器组上。可以完全由客户进行完全自主编程,或者采用Eideticom 的应用 IP,作为可立即运行的预编程解决方案来交付,后者是快速发展的计算存储市场上广受认可的领导者

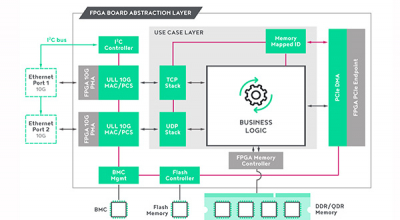

Enyx 开发框架 (nxFramework) 是一个软硬件开发环境,旨在为金融行业高效构建和维护超低时延的 FPGA 应用。nxFramework 建立在 10 年的研发基础之上,是所有 Enyx 现成解决方案的基础,可为客户提供管理一系列大量应用的工具链。

MicroBlaze可以使用AXI BRAM存放数据和指令。有些客户软件很大,需要把AXI BRAM的空间做到最大。AXI BRAM底层是Block RAM或者Ultra RAM。器件的Block RAM或者Ultra RAM个数,决定了AXI BRAM的大小。在ZCU106单板上,有312个Block RAM,有96个Ultra RAM。客户需要1MB存储空间。

来自上海科技大学的SkrSkr队脱颖而出获得亚军。作品以2019年DAC-SDC的双料冠军iSmart3的开源方案为基础,进行了量化算法、加速器以及系统三个层级的优化,实现了速度x2.4,精度+1.5%,能效x1.4

在ZYNQ的地址分配中,可以将每一个Slave接口定义为一个存储器映射,其由一个或多个地址块(目前只遇到过一个地址块),存储区和子空间映射元素组成,可以通过从属接口访问存储器映射

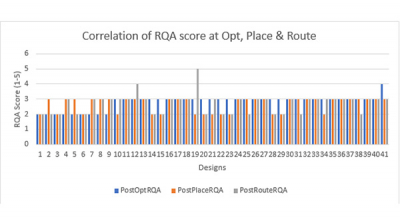

Report QoR Assessment (RQA) 用于详述您的设计 QoR 目标实现的可能性。如果此命令返回的结果与您的期望不符,那么本篇博文包含了有关您可采取的后续行动的附加信息。本篇博文不仅适合首次使用这些命令的新用户,对于有经验的用户应该同样很实用。

从2018年设立DAC-SDC开始,每年都会吸引全球百支知名研究团队参与角逐,与计算机视觉类的国际知名目标检测比赛不同,DAC-SDC对高精度、高效率的追求不仅仅停留在算法层面,其更注重考察基于软硬件协同的系统构建能力,即参赛设计不仅要提高复杂场景中小物体精准检测的能力,还需要考虑整个硬件系统在图像处理速度和功耗方面的要求

赛灵思与全球发展速度最快的硬件学习、编程与构建开发者社区Hackster.io携手推出的首届赛灵思自适应计算挑战赛一上线就收到了广大开发者和初创企业的踊跃报名。在报名过程中,也遇到了不少开发者和初创企业发来的疑问,Xilinx技术社区今天给各位带来一一解答

本例程主要使用Vivado 调用ROM IP核,用含有正弦曲线的.coe文件初始化ROM,最终通过仿真实现波形的显示。