站在巨人肩膀上创新,赛灵思15万美元重奖初创企业选手

judy 在 周二, 07/21/2020 - 17:45 提交

2020年7月21日,由集成电路自动化设计顶级会议DAC主办的第三届【低功耗目标探测系统设计挑战赛】落下帷幕,本届比赛旨在为终端设备设计高精度且高能效的物体检测系统,共吸引了来自全球多个知名研究机构共80支队伍参加,竞争非常激烈。来自北京工业大学的BJUT_Runner团队和上海科技大学的SkrSkr团队包揽冠亚军

FPGA工程师们应该都会吐槽Verilog的语法,相当的不友好,尤其是对于有很多接口的模块,像AXI4/AXI-Lite这种常用的总线接口,动不动就好几十根线,写起来是相当费劲。当然现在Xilinx推荐使用纯bd文件的方式来设计FPGA,这样HDL代码就会少了很多。但我们大多数的工程还是无法避免使用HDL来连接两个module

本章将着重讲述TLP的数据链路层组成与操作,上一篇更新应该为第五讲,数据链路层位于事务层和物理层之间,使用容错和重传机制保证了数据传输的完整性和一致性,此外,数据链路层还需要对PCIe链路层进行监控和管理。

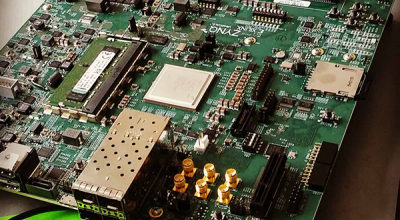

在某些情况下,比如远程工作时,可能需要访问本地不可得的器件。本篇简介教程演示了如何共享并访问位于远程实验室内的开发板或归同事所有的开发板。

AI芯片优化主要有三个方面:算法优化,编译器优化以及硬件优化。算法优化减少的是神经网络的算力,它确定了神经网络部署实现效率的上限。编译器优化和硬件优化在确定了算力的基础上,尽量最大化硬件的计算和带宽性能。经历了一年多的理论学习,开始第一次神经网络算法优化的尝试。之所以从一个FPGA开发者转向算法的学习,有几个原因

ORB特征是一种图像识别、追踪和匹配中常用的特征,大名鼎鼎的ORB-SLAM就是使用的这一特征。它提取FAST特征点,并通过特征点附近的窗口矩计算特征点的方向,含方向的FAST特征也被称为oFAST特征。对提取到的oFAST特征,进一步计算BRIEF描述子。ORB特征包含了两部分,一是特征点位置,二是它的BRIEF 256位描述子

第三届2020年人工智能大会盛大开幕,受疫情影响,今年AI大会由线下改成了线上举办,赛灵思人工智能业务高级总监姚颂带来了《AI芯片技术与产业发展路径》的演讲。

Vitis™ AI 开发环境是 Xilinx 的开发平台,适用于在 Xilinx 硬件平台(包括边缘器件和 Alveo 卡)上进行人工智能推断。它由优化的 IP、工具、库、模型和示例设计组成。Vitis AI 以高效易用为设计理念,可在 Xilinx FPGA 和 ACAP 上充分发挥人工智能加速的潜力。

医用超声拥有众多显著优势,是目前最为广泛接受和使用的诊断成像方式。在本白皮书中,赛灵思就介绍了处理器件和新的开发环境如何实时地轻松实现这些先进的成像方法。赛灵思 Versal™ 自适应计算加速平台 (ACAP) 器件与赛灵思 Alveo™ 数据中心加速卡可部署在工作站或服务器上,是实现 SA 和 PW 方法的理想硬件选择