【科普文】理解FPGA的基础知识——逻辑电路

judy 在 周二, 10/20/2020 - 09:23 提交

FPGA (Field Programmable Gate Aray,现场可编程门阵列)是一种可通过重新编程来实现用户所需逻辑电路的半导体器件。为了便于大家理解FPGA的设计和结构,我们先来简要介绍一些逻辑电路的基础知识。

FPGA (Field Programmable Gate Aray,现场可编程门阵列)是一种可通过重新编程来实现用户所需逻辑电路的半导体器件。为了便于大家理解FPGA的设计和结构,我们先来简要介绍一些逻辑电路的基础知识。

有时我们需要在设计网表的基础上微调一下逻辑,这样可以无需修改代码,也无需重新做综合,在设计调试中可以节省时间同时维持其他逻辑无任何改动。这里带大家一起体验一下Vivado 的ECO流程,以vivado自带的Example Design为例, 直接用TCL命令修改网表,在正常的寄存器路径之间加一级LUT。

ZYNQ UltraScale+ MPSoC支持支持USB3.0,其功能通过PS侧GTR接口实现。实际设计中,有时希望仅支持USB2.0即可。这里,概要描述仅需要USB2.0场景下的软硬件设计及调试过程。我们在实际设计中,采用了与ZCU102相同的USB PHY芯片(Microchip/USB3320)

Zynq UltraScale+ 的隔离设计流程主要介绍如何使用支持 Xilinx Vivado 设计套件的 Xilinx IDF 实现安全关键型设计。

通过嵌入式软核或者硬核通过AXI_Lite接口(Master)控制FPGA端引脚的GPIO。按照AXI互联机制我们知道,我们的自定义IP是通过AXI_Interconnect连接到Master端,整体的框图也比较简单,为了验证方便我们只按照红色线路径进行测试。

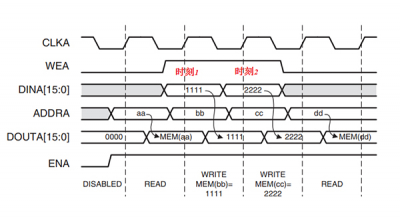

当我们调用RAMO的IP时,无论是单端口还是双端口模式,都会有个选项,可能很多人都没注意过这个选项,记得毕业季去华为面试的时候,还问过我这个问题,当时也是没答上来。后来也发现很多面试官都喜欢问这个问题,今天我们就来讲一下。

GCC编译代码时,缺省是在目录/usr/include查找头文件,在目录/usr/lib查找库文件。如果是交叉编译,就不能在主机的目录下查找头文件和库文件,因为它们包含的是主机的应用程序的文件。我们需要指定目标单板的头文件和库文件。对于这种需求,GCC使用选项sysroot来实现

从 Vivado 2018.3 开始,Vivado 隔离验证器 (VIV) 将与 Vivado 版本集成,支持 UltraScale+ 器件(包括 Zynq UltraScale+)。本文档主要介绍如何在 FPGA/PL 设计中使用新的 Vivado 隔离验证器 (VIV) 来验证隔离。

本文将从代码风格,时序修正,工程设置等几个方面介绍本人的实践经验,希望让各位初学者快速提高,也希望FPGAer能给出宝贵建议。

Integrated Block for PCIe® 核是高可靠性、高带宽、高可扩展性的串行互连构建块,适合与 UltraScale+™ 器件配合使用。该核可对 UltraScale+ 器件中提供的集成块进行例化。