洗去浮华,价值浮现:探秘AI 芯片技术与产业发展之路

judy 在 周五, 07/17/2020 - 10:27 提交

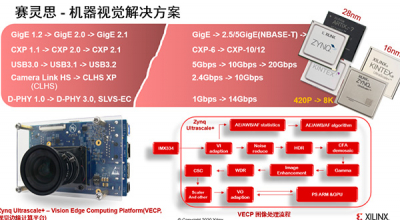

纵观 AI 发展,2020 年的我们身处何地?是黄金时代?还是寒冬前兆?AI 芯片现状如何,未来将走向何方?赛灵思将为 AI 发展带来什么价值?

且听原深鉴科技 90 后 CEO 姚颂(现赛灵思人工智能高级总监)为您解读

纵观 AI 发展,2020 年的我们身处何地?是黄金时代?还是寒冬前兆?AI 芯片现状如何,未来将走向何方?赛灵思将为 AI 发展带来什么价值?

且听原深鉴科技 90 后 CEO 姚颂(现赛灵思人工智能高级总监)为您解读

本文提供了此次演讲的音频、视频以飨读者,同时用文字的形式为大家分享酆毅演讲内容要点,献给所有致力于解决智能制造升级转型挑战的人们。

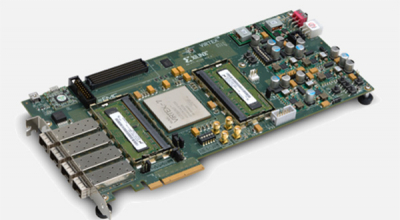

一些 5G 系统的制造商正在转向更高水平的硬件集成,并在片上系统(SoC)设备中整合射频转换器和基带处理引擎,以解决功耗和电路板空间问题。虽然这种集成有好处,但负责这些系统表征的工程师面临着访问数据的新挑战,因为之前的独立射频数据转换器现在将与 FPGA 和处理器在同一芯片上进行组合

FPGA 器件凭借强大的功能、灵活性和即时可用性形成极具吸引力的业务驱动力,掀起了一场广泛采用 FPGA 来实现系统 PCB 设计的浪潮。很显然,FPGA 器件的上市时间优势和容量/性能特性已兑现其产品承诺,成为更多资本资源密集型定制 IC/ASIC 解决方案的可行替代方案

Zynq® UltraScale+™ RFSoC ZCU208 评估套件是面向开箱即用评估及前沿应用开发的理想 RF 测试平台。该套件包含 UltraScale+ RFSoC ZU48DR,其集成 8 个 14 位 5GSPS ADC、8 个 14 位 10GSPS DAC 以及 8 个软决策前向纠错 (SD-FEC) 内核,专为快速启动 RF 类应用而设计。

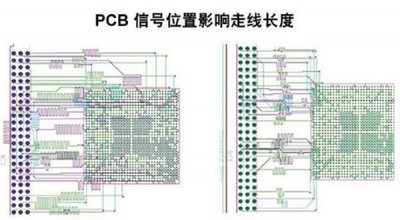

在进行FPGA硬件设计时,引脚分配是非常重要的一个环节,特别是在硬件电路上需要与其他芯片通行的引脚。Xilinx FPGA从上电之后到正常工作整个过程中各个阶段引脚的状态,会对硬件设计、引脚分配产生非常重要的影响。这篇专题就针对FPGA从上电开始 ,配置程序,到正常工作整个过程中所有IO的状态进行分析。

2019 XDF 演示文稿:RFSoC 工具和多频带支持示例

在上篇文章中了整理了一些针对开发者参加本次挑战赛的常见问题并解答,本期文章将对初创企业参赛的一些常见问题整理并解答。

这大半年一直在做一个高速板卡FPGA相关的方方面面的工作,包括前期FPGA架构布局设计,管脚验证,后期实现资源优化,最后到板卡调试。过程曲折艰辛,但是也收获良多。今天在这里记录下工作中零零散散的记录下来。

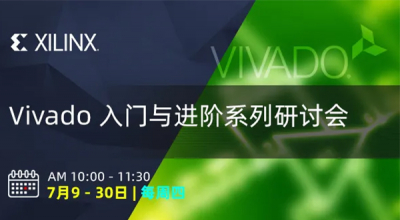

本次系列研讨会将由赛灵思战略应用高级工程师 Lauren Gao(高亚军)带领大家从基础到进阶,一站式领略 Vivado 这款神奇的开发工具。