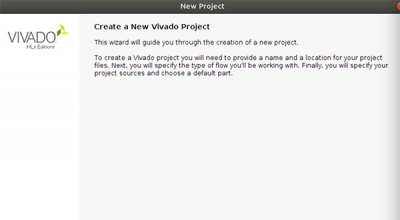

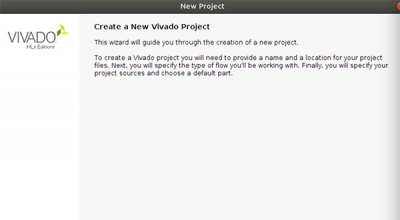

第一个Xilinx Vitis IDE入门helloworld程序

joycha 在 周二, 11/10/2020 - 16:46 提交

第一个Xilinx Vitis IDE入门helloworld程序

第一个Xilinx Vitis IDE入门helloworld程序

在读取 IBERT 的自适应环路代码时,出现了与 DMONITOROUT 的期望值不同的值。对于 UltraScale+ GTH 收发器而言,签名了一些 RX 均衡自适应环路。用户指南的数字监控器 (DMON) 部分向用户展示了如何读取自适应环路的当前状态。

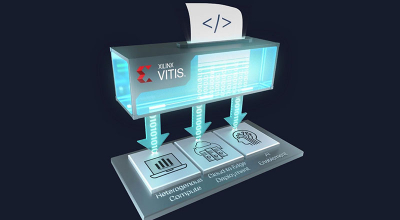

本博文介绍Vitis AI1.1 系列软件安装教程。

Deep-AI 的软件解决方案在 Xilinx Alveo PCIe 卡上运行,从而消除了对 GPU 的需求,并且与 GPU 相比,其性能功耗比或性价比提高了 10 倍。

区别于传统的一根信号线一根地线的做法,差分传输在两根线上都传输信号,这两个信号的振幅相同,相位相反,在这两根线上的传输的信号就是差分信号。信号接收端通过比较这两个电压的差值来判断发送端发送的逻辑状态。在电路板上,差分走线必须是等长、等宽、紧密靠近、且在同一层面的两根线。

AXI4-Stream跟AXI4的区别在于AXI4-Stream没有ADDR接口,这样就不涉及读写数据的概念了,只有简单的发送与接收说法,减少了延时,允许无限制的数据突发传输规模。AXI4-Stream的核心思想在于流式处理数据。

OneSpin 工具可验证综合和实现过程(即 RTL 和综合网表)中任意两个步骤之间的功能等效性。本答复记录涵盖有关 OneSpin 支持版本的详细信息,以及设置 OneSpin 以测试 Vivado 综合生成的网表的基本流程。

要查找有效 Xilinx 部件号的出口控制分类号 (ECCN),请使用以下工具:

https://xapps9.xilinx.com/ebsextn/gtc

有关有效 Xilinx 部件编号,请参阅以下产品数据表:

本视频将为医疗设备架构师和设计人员介绍用于工业自动化及其它高可靠性市场的功能安全性和网络安全性方法,以及 Xilinx 技术用于医疗设备设计流程基于风险管理的环节的原理,其可在加速上市进程的同时,创建更稳健的设计。

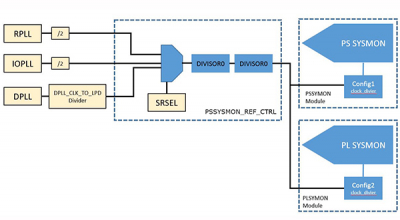

Zynq UltraScale+ MPSoC TRM 包含一个详细介绍 PS 及 PL SYSMON 时钟的部分。本答复记录详细描述了 PS 和 PL SYSMON 的时钟基础架构。